Method and apparatus for adjusting phases of EMMC interface and NAND interface

A phase adjustment and interface technology, applied in the field of phase adaptive adjustment, can solve problems such as waste of material resources and human resources, general adaptation of circuit boards to nand flash memory, and wrong sampling, so as to reduce manpower and material resources, reduce design difficulty, and adjust high precision effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

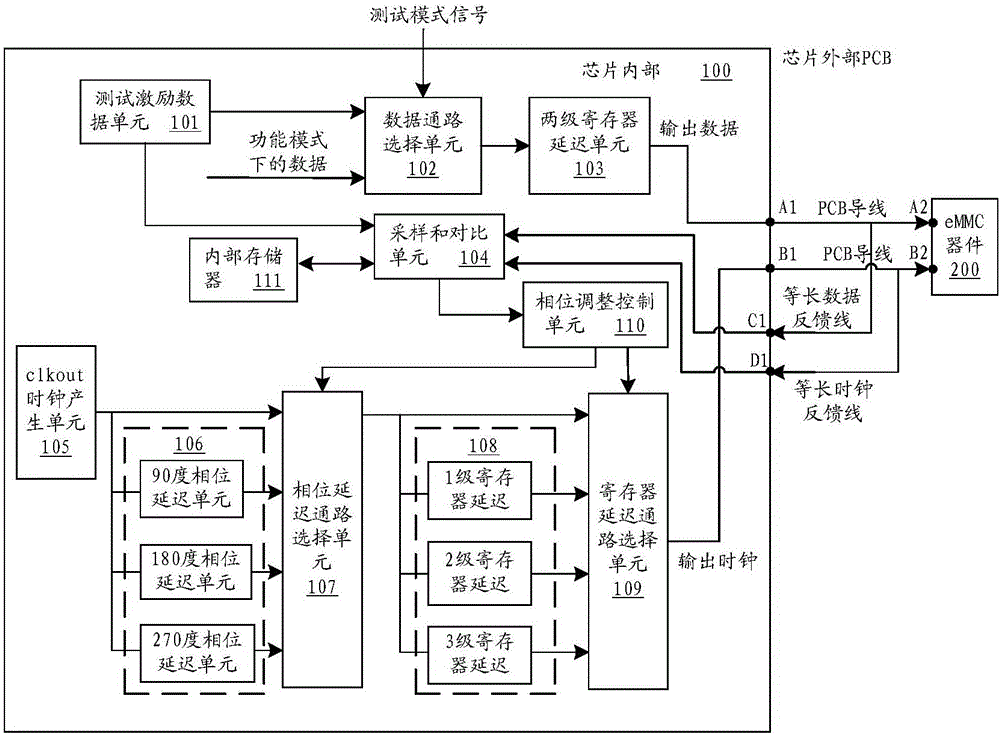

[0041] see image 3 Shown, EMMC interface phase adjustment method of the present invention comprises the following steps:

[0042] (1) Adaptive training of the PCB board before the first normal working mode, first control the test mode signal to be set to be valid;

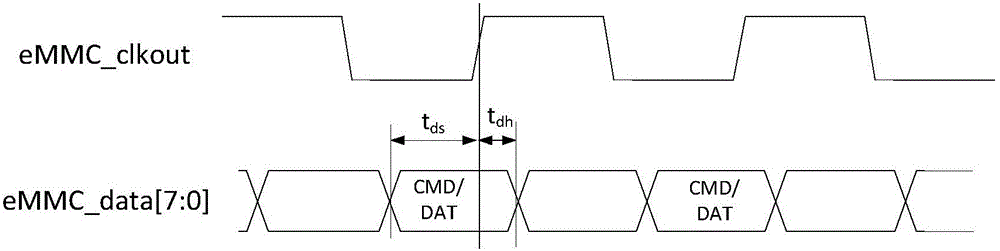

[0043] (2) The test excitation data is strobed and sent out according to the transmission clock frequency of the pre-stored data sequence, and sent to the data pin port of the main control chip after being delayed by two-stage registers. Then it is transmitted to the data pin of the EMMC device through the PCB wire feet; at the same time

[0044] The data transmission clock of EMMC is output to the clock pin port of the main control chip after phase delay and register delay in sequence, and then transmitted to the clock pin of the EMMC device through the PCB wire;

[0045] (3) by controlling the phase delay and the register delay, until the internal phase delay configuration of the chip that best matches the PCB...

Embodiment 2

[0092] see Figure 4 Shown, NAND interface phase adjustment method of the present invention comprises the following steps:

[0093] (1) Adaptive training of the PCB board before the first normal working mode, first control the test mode signal to be set to be valid;

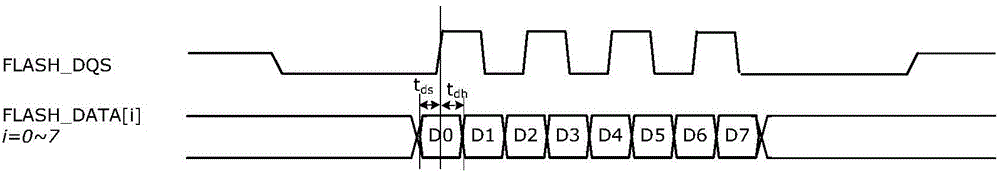

[0094] (2) The test stimulus data is strobed and sent out according to the transmission clock frequency of the pre-stored data sequence, and sent to the data pin port of the main control chip after being delayed by two-stage registers. Then the data is transmitted to the NAND flash memory device through the PCB wire pin feet; at the same time

[0095] The data transmission clock of the NAND flash memory is output to the clock pin port of the main control chip after phase delay and register delay in sequence, and then transmitted to the clock pin of the NAND flash memory device through the PCB wire;

[0096] (3) by controlling the phase delay and the register delay, until the internal phase delay configuration o...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com