A FPGA implementation system and method for oversampling data clock recovery

A technology of data clock and implementation method, which is applied in the direction of data error detection, electrical digital data processing, response error generation, etc. with redundancy in operation, can solve problems such as insufficient GE port dedicated pins, and achieve reduced cost effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

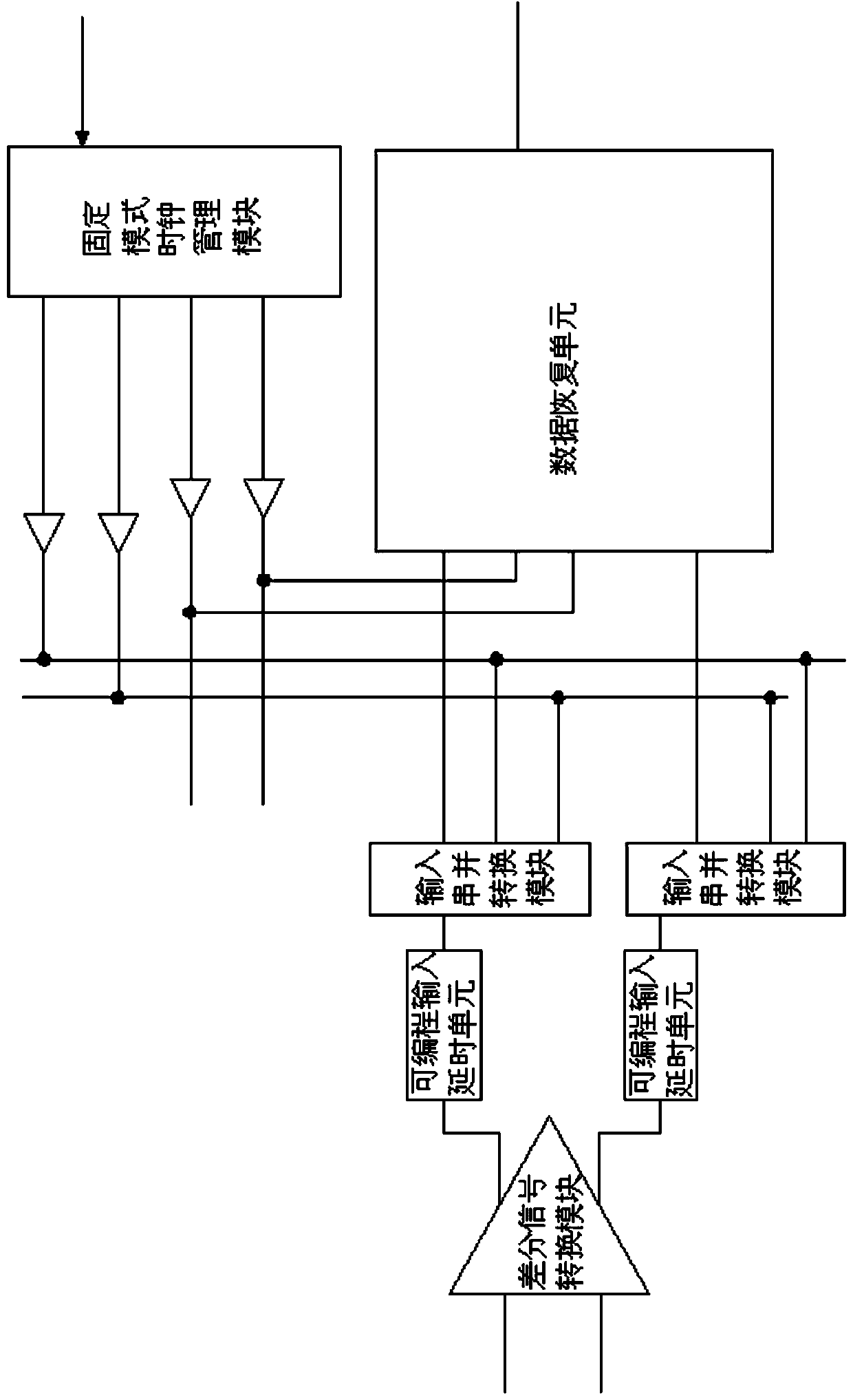

[0042] An FPGA implementation system for oversampling data clock recovery, such as figure 1 As shown, it includes a differential signal conversion module, a programmable input delay unit, an input serial-to-parallel conversion module and a fixed-mode clock management module arranged in the FPGA, the differential signal conversion module is connected to a programmable input delay unit, and the The programmable input delay unit is connected to the input serial-to-parallel conversion module, and the input serial-to-parallel conversion module is connected to the fixed-mode clock management module.

[0043] The differential signal conversion module is used to buffer the input differential signal sent into the FPGA from the outside and divide it into two differential signals inside the FPGA;

[0044] The programmable input delay unit delays the differential signal inside the FPGA;

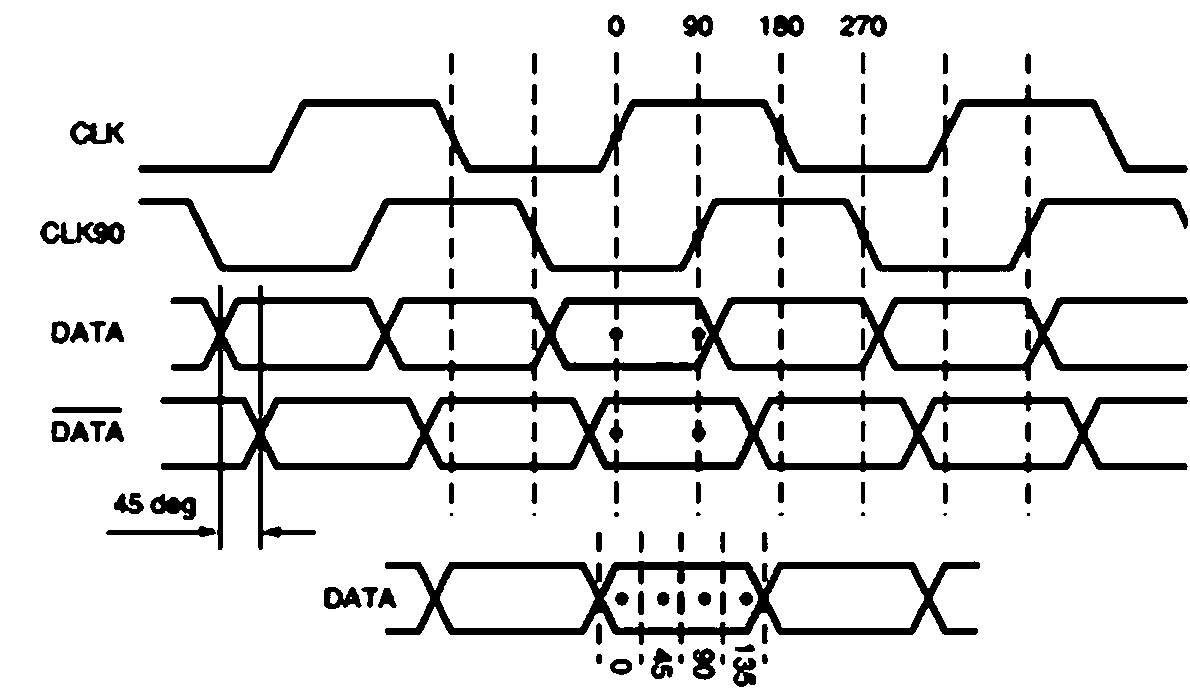

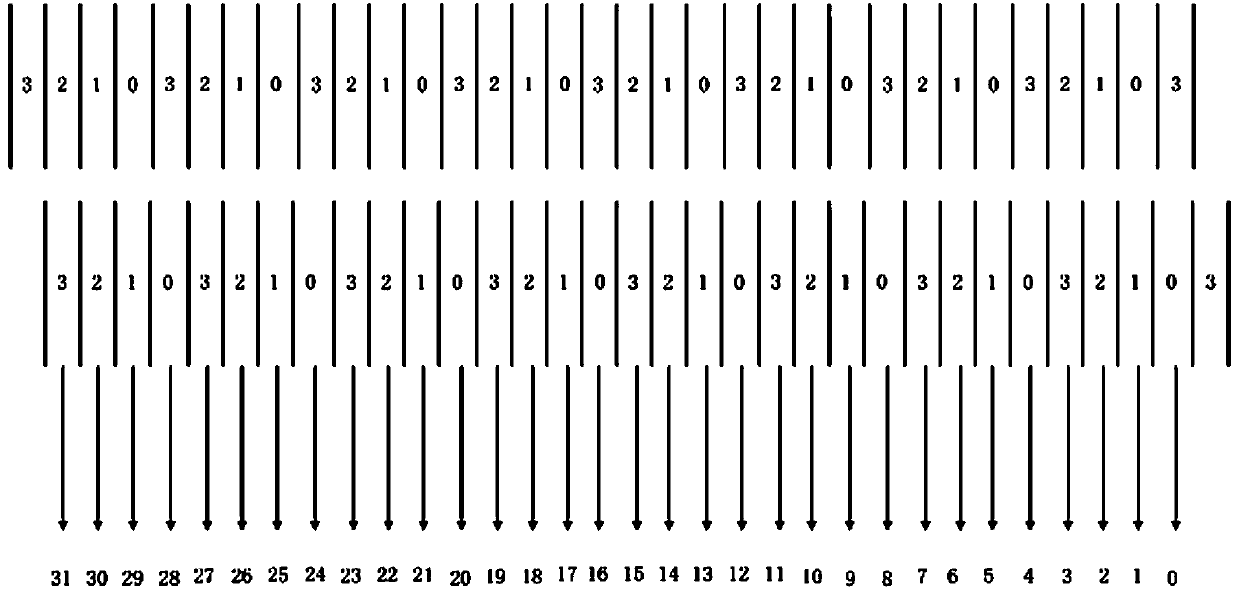

[0045]The input serial-to-parallel conversion module samples the signal output in the programmable i...

Embodiment 2

[0048] This embodiment is further optimized on the basis of the above embodiments, such as figure 1 As shown, further in order to better realize the system of the present invention, the data collected in the input serial-to-parallel conversion module can be recovered, and the following setting method is particularly adopted: a data recovery unit is also included, and the data recovery unit It is connected to the input serial-to-parallel conversion module, and the fixed-mode clock management module is also connected to the data recovery unit.

Embodiment 3

[0050] This embodiment is further optimized on the basis of the above embodiments, such as figure 1 As shown, further in order to better realize the system of the present invention, the following setting method is adopted in particular: the programmable input delay unit is two and the output signal between the two programmable input delay units exists 45 ° phase difference, the two programmable input delay units are connected to the differential signal conversion module and the input serial-to-parallel conversion module.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More