Acceleration processing unit based on convolutional neural network and array structure thereof

A convolutional neural network and processing unit technology, applied in the field of accelerated processing units and array structures, can solve the problems of increased processing speed, high power consumption, large chip area of accelerated processing units, etc., and achieve the goal of small on-chip area and reduced use Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

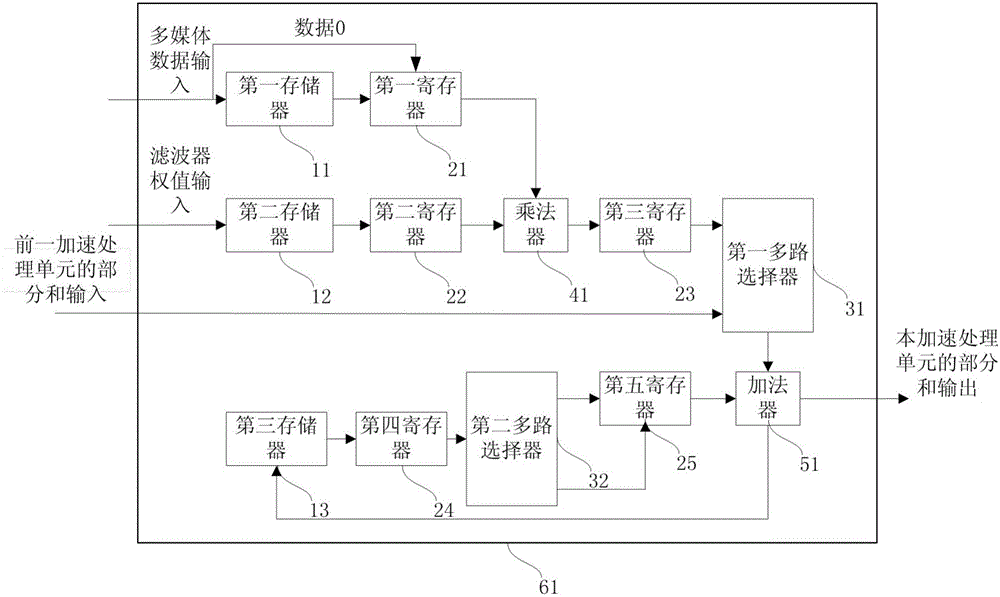

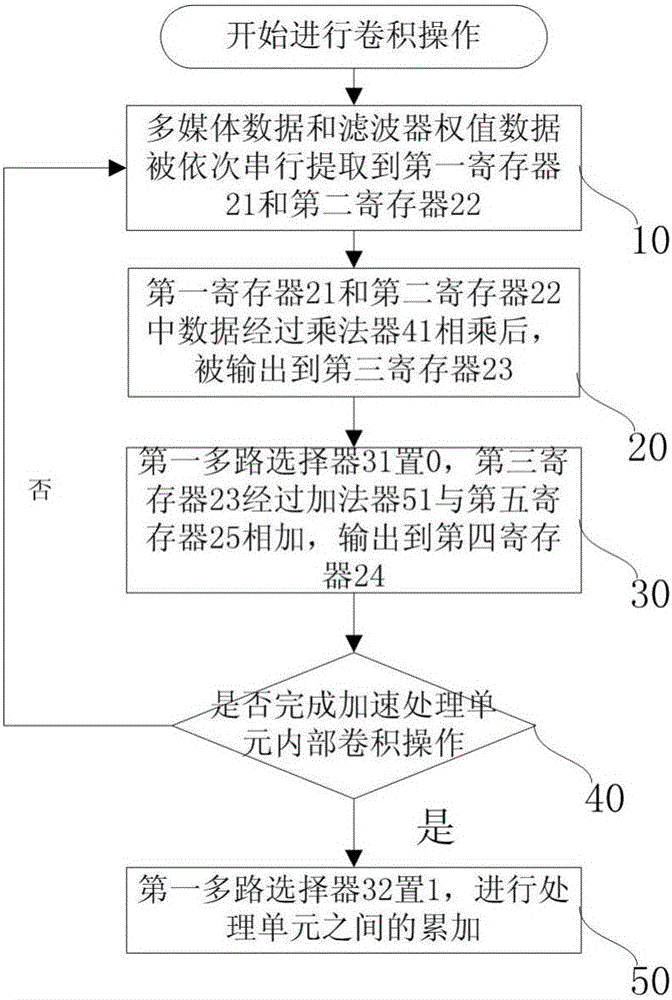

[0031] Please refer to figure 1 , the present embodiment provides an accelerated processing unit based on a convolutional neural network. The accelerated processing unit 61 includes a first register 21, a second register 22, a third register 23, a fourth register 24, a fifth register 25, and a multiplier 41 , adder 51 and first multiplexer 31 and second multiplexer 32.

[0032] The first register 21 is connected to an input end of the multiplier 41 , and the first register 21 is used for inputting multimedia data and sending the multimedia data to the multiplier 41 . The second register 22 is connected to the other input terminal of the multiplier 41 , and the second register 22 is used to input the filter weight and send the filter weight to the multiplier 41 . The output terminal of the multiplier 41 is connected to the third register 23 for multiplying the multimedia data and the filter weight, and sending the multiplied result to the third register 23 .

[0033] The firs...

Embodiment 2

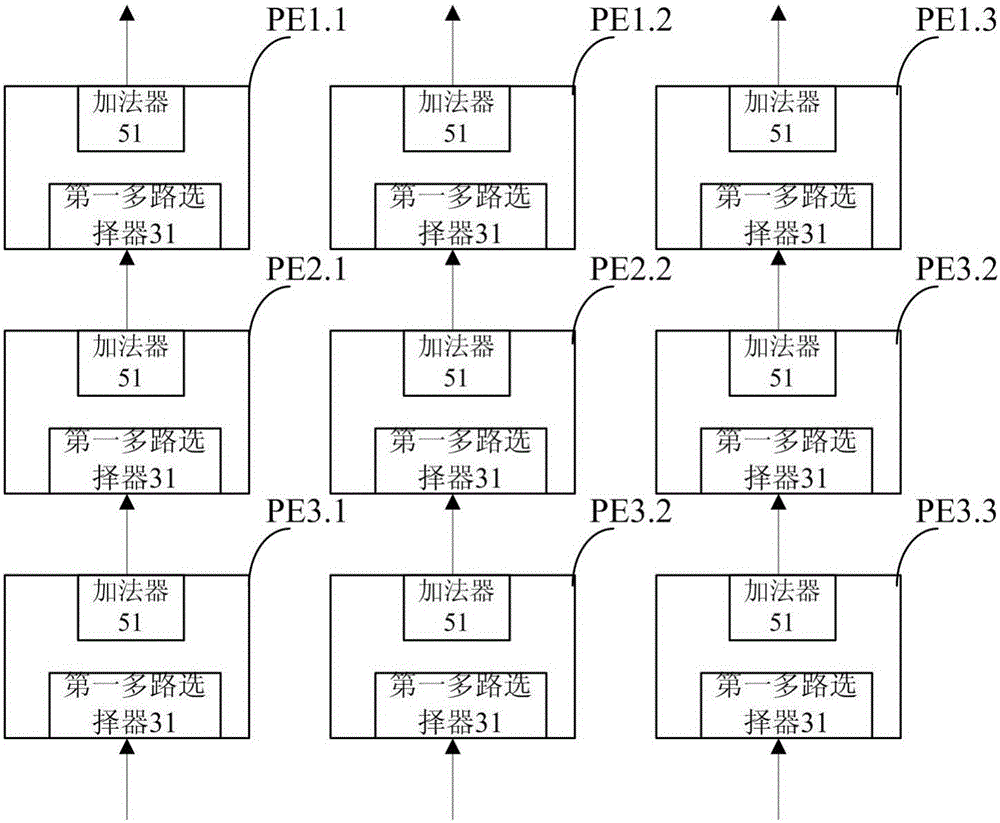

[0047] Please refer to Figure 3 to Figure 5 , showing an array structure based on a convolutional neural network, including multiple accelerated processing units, the multiple accelerated processing units are in the form of a matrix with M rows and N columns, where M and N are integers greater than or equal to 1 , the accelerated processing units of each column are connected back and forth.

[0048] In this embodiment, multiple accelerated processing units are in the form of a matrix of 3 rows and 3 columns. In each column, the output end of the adder of the previous accelerated processing unit is connected to the first multiplexer of the next accelerated processing unit. Three ends.

[0049] In the accelerated processing units in the same row, the input filter weights are the same; in the accelerated processing units located in the same diagonal line, the input local data are the same.

[0050] In the accelerated processing units of different rows, the input filter weights...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More