Forming method of semiconductor structure

A semiconductor and structural part technology, applied in the field of semiconductor structure formation, can solve the problems of dummy gate structure damage, affecting the performance of semiconductor structures, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

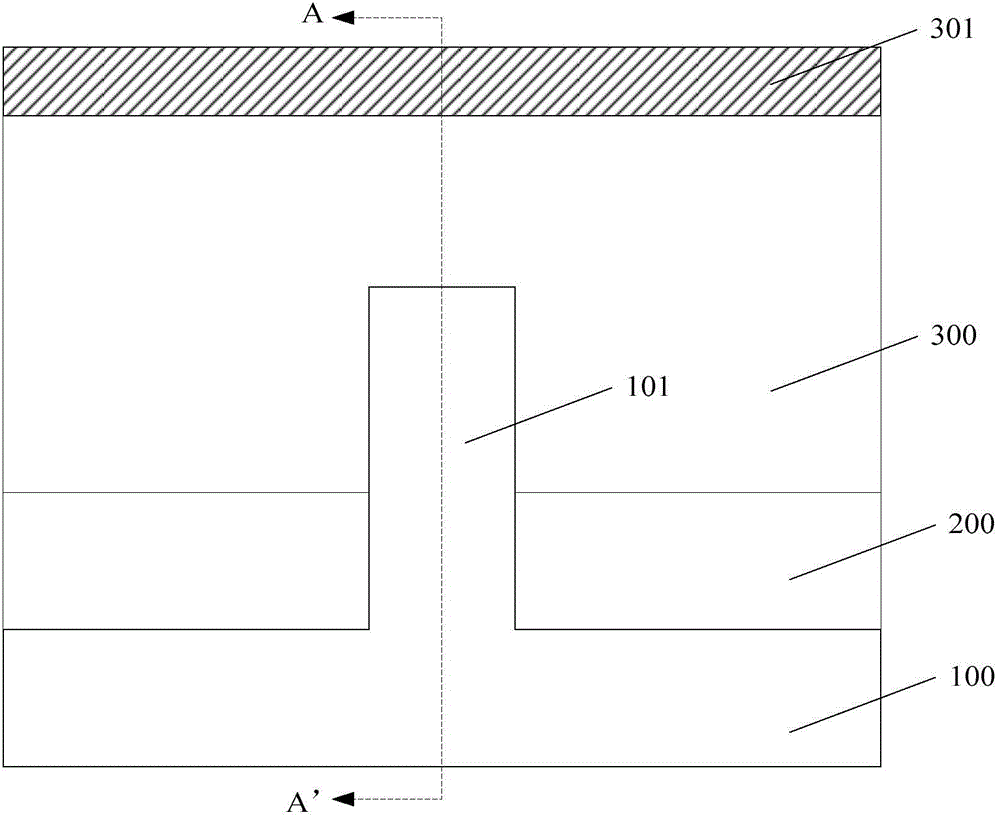

[0034] As mentioned in the background art, the performance of the semiconductor structure formed in the prior art needs to be further improved.

[0035] Research has found that after the formation of the dummy gate structure, sidewalls are usually formed on the surface of the side walls of the dummy gate structure, and a mask layer is provided on the top of the dummy gate structure to protect the surface of the dummy gate structure. In the process of etching the fins on both sides of the dummy gate structure to form grooves, the sidewalls on both sides of the dummy gate structure and the mask layer on the top of the dummy gate structure are often damaged, resulting in the exposure of the surface of the dummy gate structure. When the stress material is filled in the groove subsequently, the stress material will also be formed when the dummy gate structure appears, and the dummy gate structure will be removed later to form the gate structure, which will cause an electrical gap be...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More