FinFET (Fin Field-Effect Transistor) split gate structure complementary symmetric logic-based Inclusive OR-exclusive OR circuit

A complementary and symmetrical technology, applied in the same-or-exclusive-or circuit field, can solve problems such as insufficient drive capability, large number of FinFET tubes, large circuit power consumption and time delay, etc., to reduce layout area and power consumption, and reduce leakage current Effects of power consumption, power reduction, and latency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

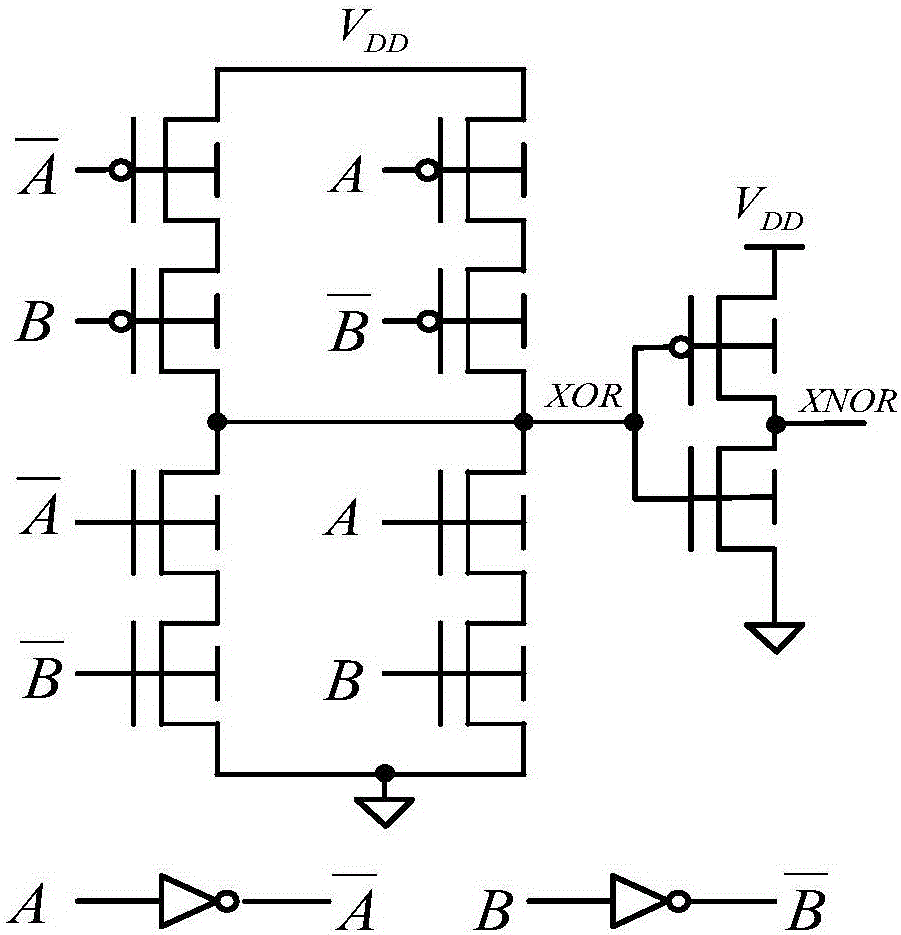

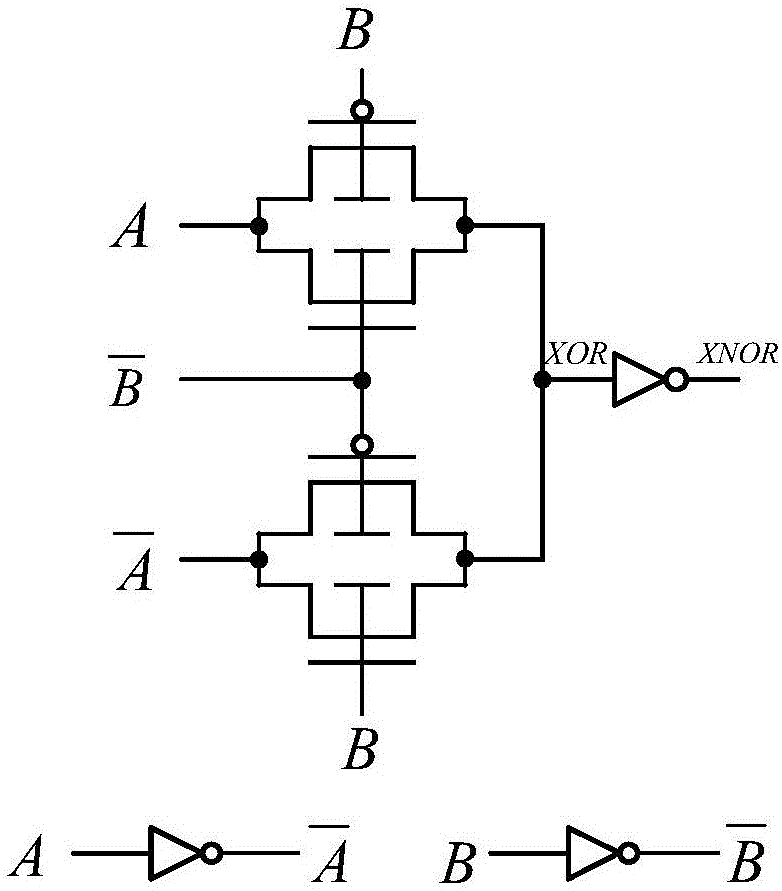

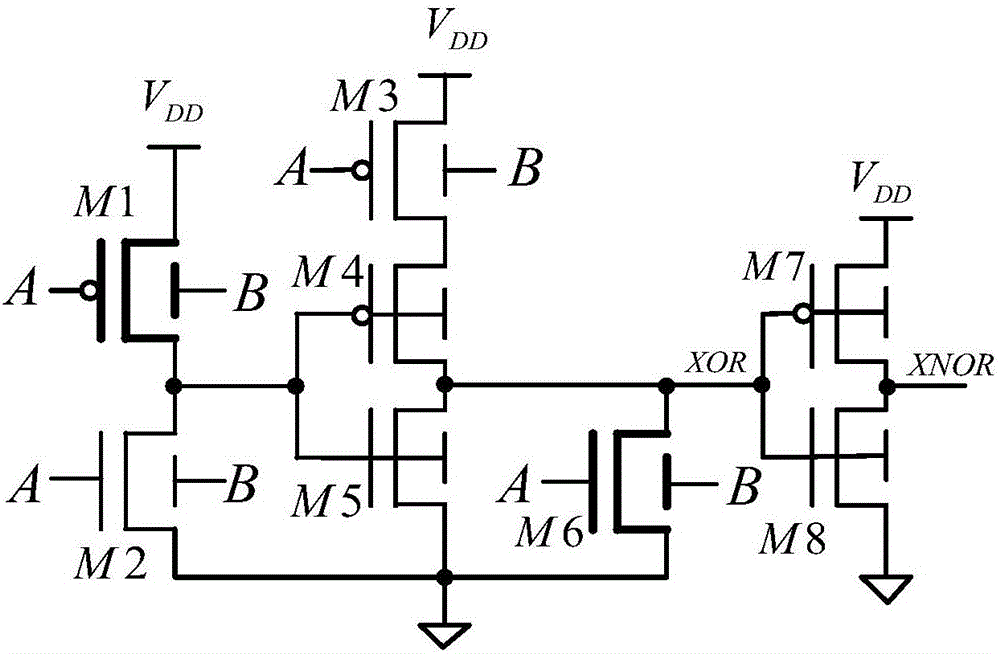

[0016] Embodiment one: if image 3As shown, a NOR and XOR circuit based on FinFET divided-gate structure complementary symmetric logic, including a first FinFET tube M1, a second FinFET tube M2, a third FinFET tube M3, a fourth FinFET tube M4, and a fifth FinFET tube M5 , the sixth FinFET tube M6, the seventh FinFET tube M7 and the eighth FinFET tube M8, the first FinFET tube M1, the third FinFET tube M3, the fourth FinFET tube M4 and the seventh FinFET tube M7 are P-type FinFET tubes, the second The FinFET tube M2, the fifth FinFET tube M5, the sixth FinFET tube M6 and the eighth FinFET tube M8 are N-type FinFET tubes, the number of fins of the first FinFET tube M1 and the sixth FinFET tube M6 is 3, and the number of fins of the second FinFET tube M2, the third FinFET tube M3, the fourth FinFET tube M4, the fifth FinFET tube M5, the seventh FinFET tube M7 and the eighth FinFET tube M8 have 1 fin; the source of the first FinFET tube M1, the third The source of the FinFET M3 a...

Embodiment 2

[0017] Embodiment two: if image 3 As shown, a NOR and XOR circuit based on FinFET divided-gate structure complementary symmetric logic, including a first FinFET tube M1, a second FinFET tube M2, a third FinFET tube M3, a fourth FinFET tube M4, and a fifth FinFET tube M5 , the sixth FinFET tube M6, the seventh FinFET tube M7 and the eighth FinFET tube M8, the first FinFET tube M1, the third FinFET tube M3, the fourth FinFET tube M4 and the seventh FinFET tube M7 are P-type FinFET tubes, the second The FinFET tube M2, the fifth FinFET tube M5, the sixth FinFET tube M6 and the eighth FinFET tube M8 are N-type FinFET tubes, the number of fins of the first FinFET tube M1 and the sixth FinFET tube M6 is 3, and the number of fins of the second FinFET tube M2, the third FinFET tube M3, the fourth FinFET tube M4, the fifth FinFET tube M5, the seventh FinFET tube M7 and the eighth FinFET tube M8 have 1 fin; the source of the first FinFET tube M1, the third The source of the FinFET M3 ...

Embodiment 3

[0019] Embodiment three: as image 3 As shown, a NOR and XOR circuit based on FinFET divided-gate structure complementary symmetric logic, including a first FinFET tube M1, a second FinFET tube M2, a third FinFET tube M3, a fourth FinFET tube M4, and a fifth FinFET tube M5 , the sixth FinFET tube M6, the seventh FinFET tube M7 and the eighth FinFET tube M8, the first FinFET tube M1, the third FinFET tube M3, the fourth FinFET tube M4 and the seventh FinFET tube M7 are P-type FinFET tubes, the second The FinFET tube M2, the fifth FinFET tube M5, the sixth FinFET tube M6 and the eighth FinFET tube M8 are N-type FinFET tubes, the number of fins of the first FinFET tube M1 and the sixth FinFET tube M6 is 3, and the number of fins of the second FinFET tube M2, the third FinFET tube M3, the fourth FinFET tube M4, the fifth FinFET tube M5, the seventh FinFET tube M7 and the eighth FinFET tube M8 have 1 fin; the source of the first FinFET tube M1, the third The source of the FinFET M...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More