Integrated circuit testing method

A technology of integrated circuits and testing methods, applied in the field of semiconductors, can solve problems such as the overall performance degradation of integrated circuits, and achieve the effect of preventing electrical breakdown

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

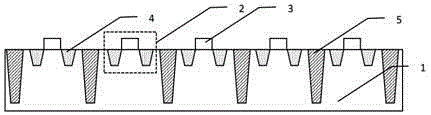

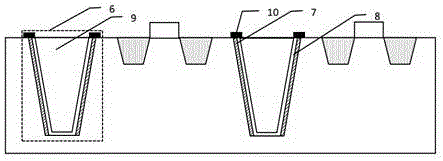

[0019] see figure 2 , the present invention provides an integrated circuit testing structure, comprising: a substrate 1; a plurality of discrete semiconductor devices 2 formed on the upper surface of the substrate 1; , a plurality of trench structures 6 located in the substrate 1, each of the plurality of trenches has a U-shaped cross-section, has a rectangular opening in plan view, and is adjacent to two opposite sides of the plurality of semiconductor devices And the bottom surface at the bottom of the groove; the two opposite electrode plate layers 7 arranged on the side; the trench isolation material 9 filled in the plurality of grooves and located on the electrode plate layer. It also includes a silicon carbide layer 8 between the electrode plate layer and the trench isolation material.

[0020] Wherein, the substrate 1 is a wafer or a silicon substrate, and has a certain thickness, which can form multiple devices and their auxiliary parts in post-production; the electr...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More