Rc oscillator based on delay-free comparator

A technology of oscillator and comparator, applied in the field of RC oscillator

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

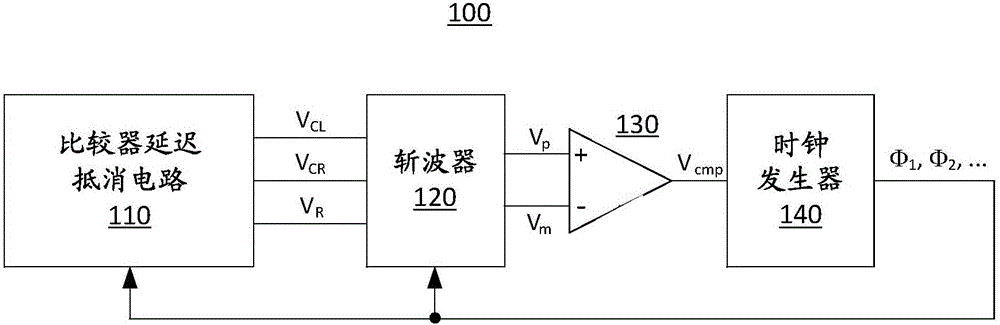

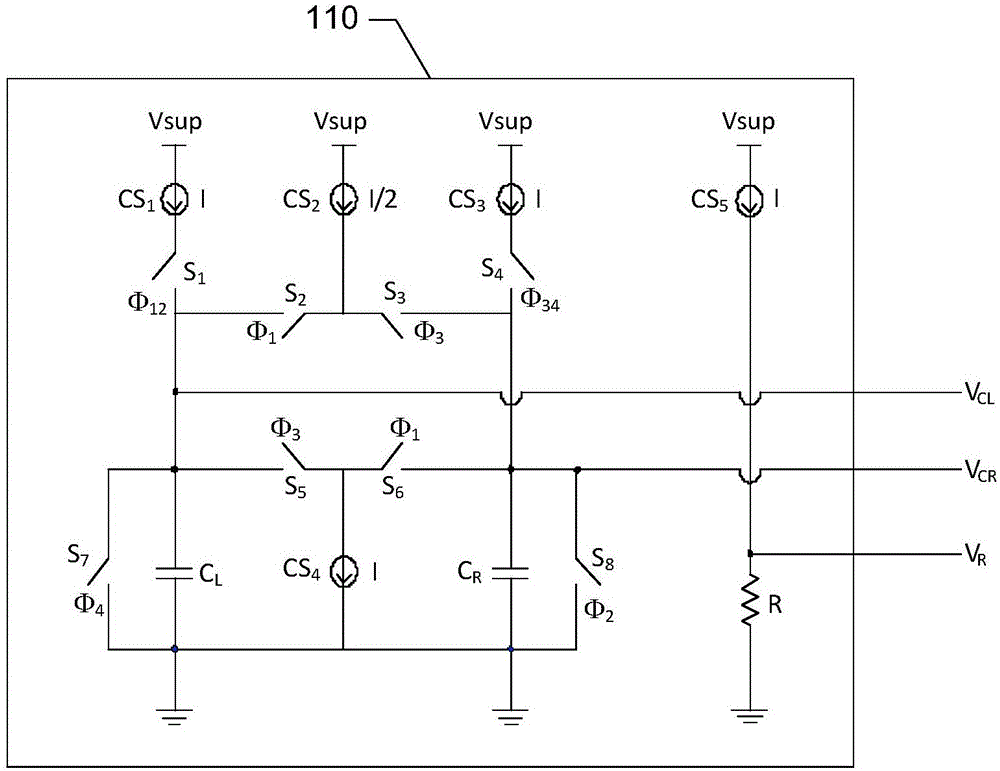

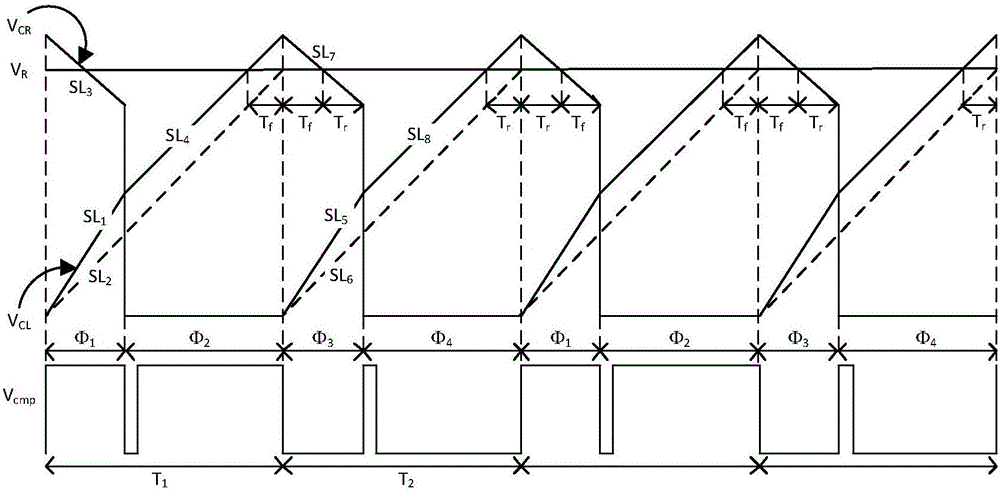

[0024] As mentioned above, RC oscillator is an important block in VLSI system. This RC oscillator provides the reference clock when the crystal oscillator is unavailable or shut down for power saving purposes. However, the frequency accuracy of an RC oscillator is limited by RC process variations, resistor temperature coefficients, and comparator delay variations. In traditional RC oscillator designs, the offset voltage of the comparator is canceled by comparing the two comparator voltages with the resistor voltage. When the voltage on the first capacitor ramps up as the first capacitor is charged by the first charging current, the second capacitor is shorted to ground. A comparator compares the first capacitor voltage to the resistor voltage. At the transition of the comparator, the first capacitor is shorted to ground and the voltage on the second capacitor ramps up as the second capacitor is charged by the second charging current. The comparator now compares the second c...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More