A method of erasing NAND Flash

An erasing block and soft erasing technology, applied in information storage, static memory, instruments, etc., can solve the problems of inability to move the P-type semiconductor substrate 23 and fix it, so as to reduce charge traps and prolong service life , to ease the effect of offset

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

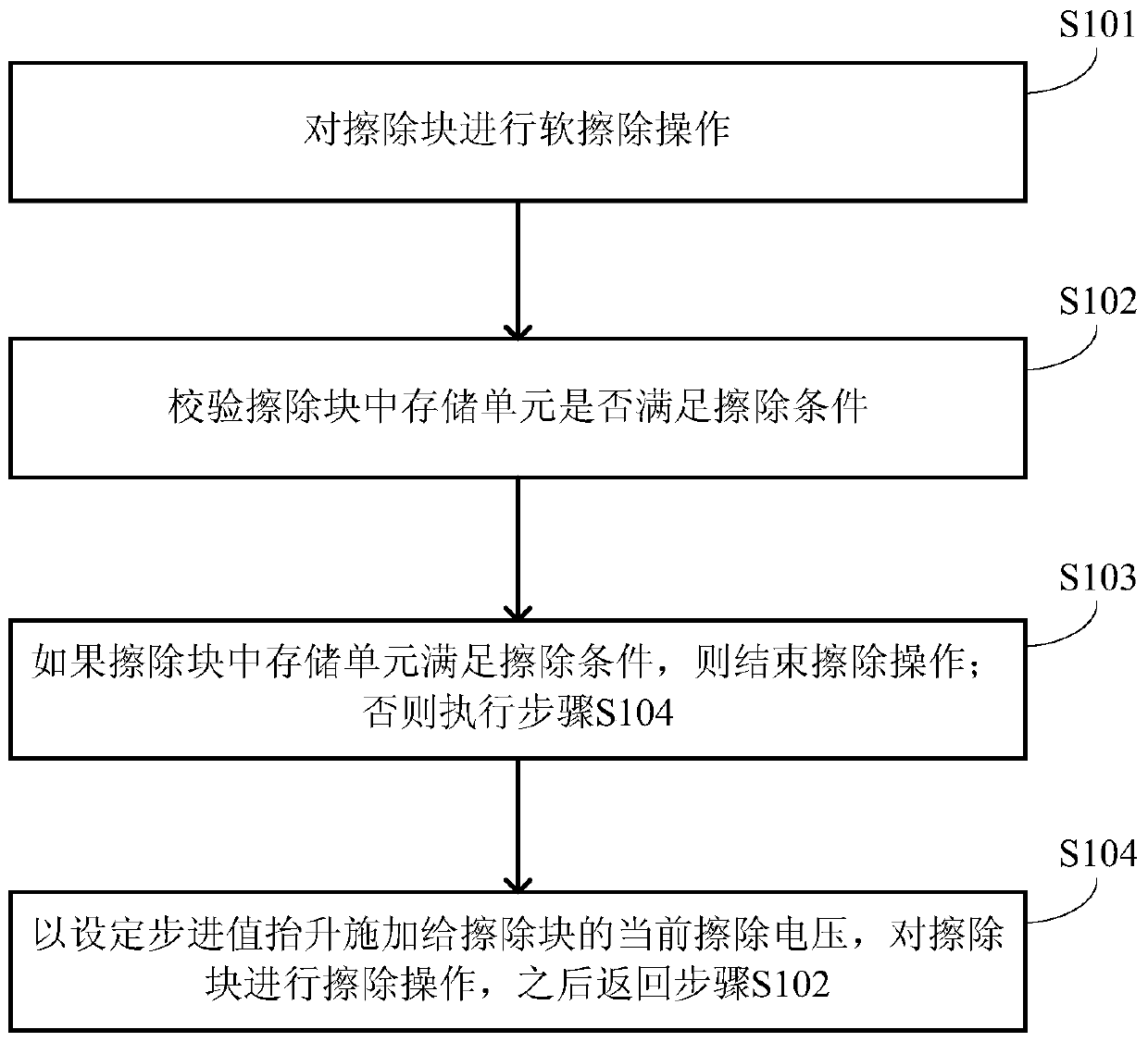

[0032] image 3 The flow chart of a kind of erasing method of Nand Flash that the embodiment 1 of the present invention provides, this method is carried out by Nand Flash, is a kind of improvement to existing erasing method, as image 3 As shown, the method includes:

[0033] Step S101 , performing a soft erase operation on the erase block.

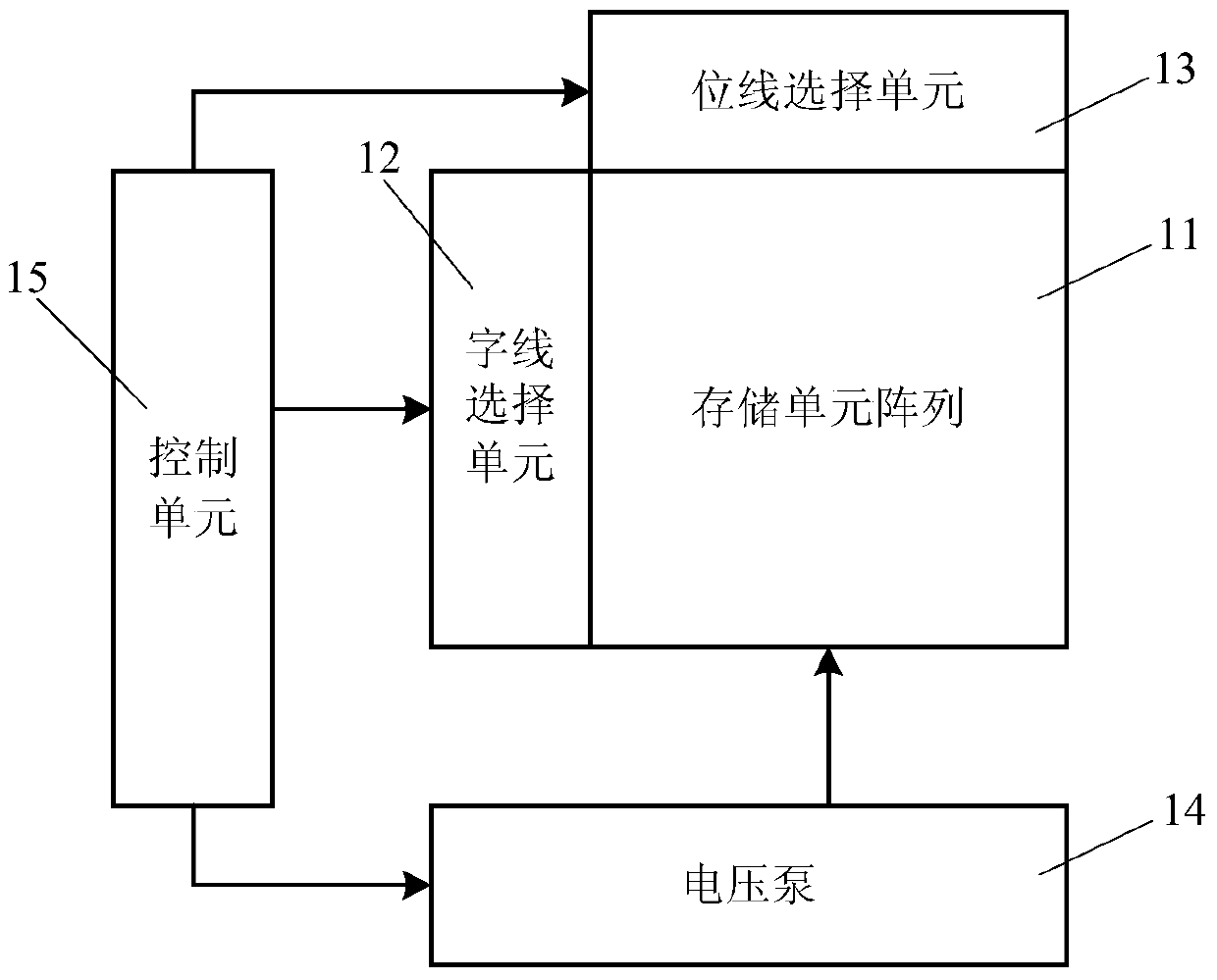

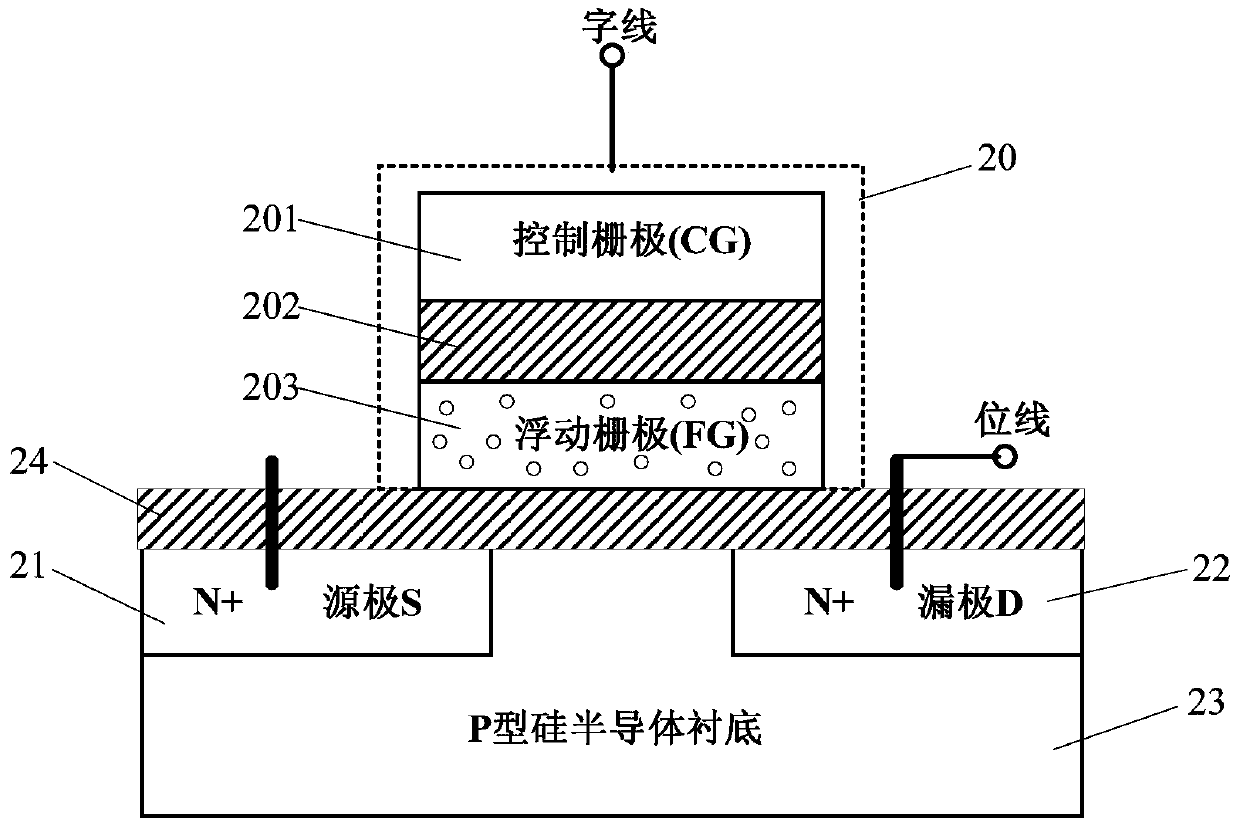

[0034] In this embodiment, the erasing block may specifically be a memory cell block used for erasing operations in the memory cell array of Nand Flash. The erasing operation is carried out in units of storage unit blocks, the storage unit array of the Nand Flash is composed of a plurality of storage unit blocks, the storage unit block is composed of a plurality of storage unit pages, and the storage unit pages are composed of a plurality of storage unit pages. Storage cells are connected in rows and columns. In a memory cell page, each row is connected by a plurality of memory cells with a word line, and each column is connected with ...

Embodiment 2

[0051] Figure 4 The flow chart of the erasing method of a kind of Nand Flash that the embodiment of the present invention provides, present embodiment optimizes on the basis of above-mentioned embodiment, in the present embodiment, the step is to erase block and carry out soft erase operation optimization as : a. Apply an initial soft erase voltage to the erase block, and continue to apply pressure within a preset time; b. Raise the current soft erase voltage with a set voltage increment value, and continue to apply it within the preset time. c. If the current soft erase voltage value does not reach the preset voltage value, repeat step b.

[0052] Further, before the step of applying the initial soft erase voltage for the erase block, a step is added:

[0053] Based on the control unit in Nand Flash, the memory block to be erased is selected through word line selection and bit line selection, which is recorded as an erase block.

[0054] Correspondingly, the method of this...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More