Caching method and device for microcontroller

A high-speed cache and micro-controller technology, applied in the direction of instruments, memory systems, electrical digital data processing, etc., can solve the problems of low hit rate of instruction data and inflexible usability of high-speed cache

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

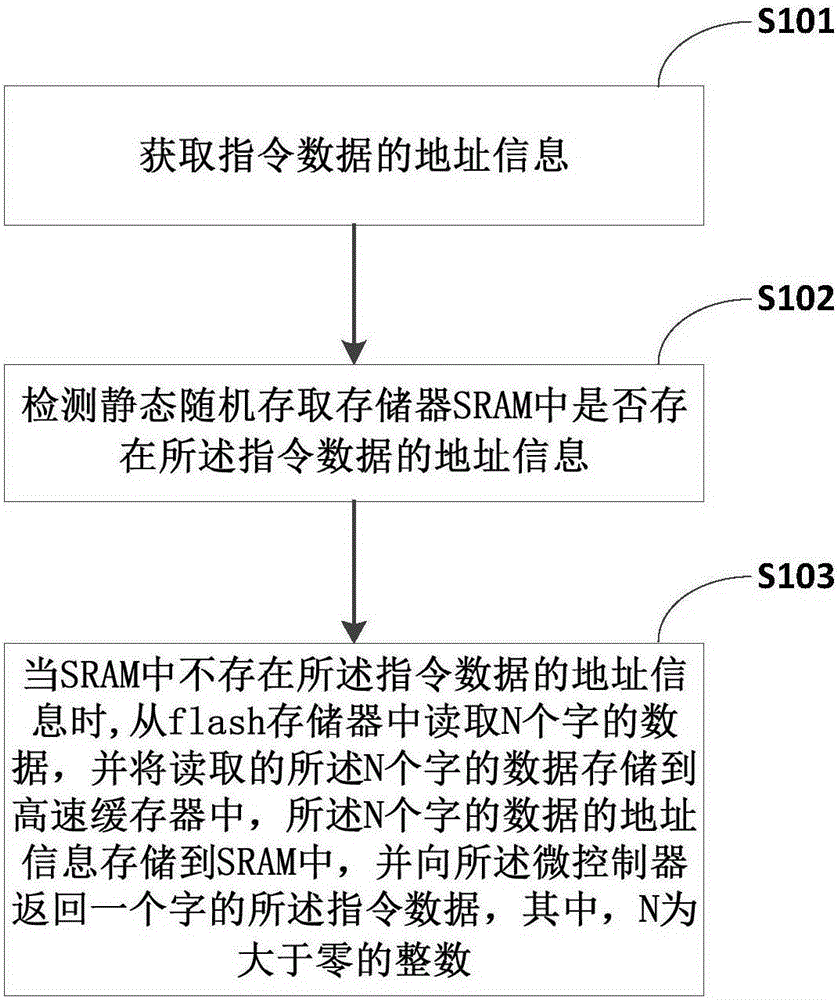

[0021] figure 1 The implementation flow of the microcontroller cache method provided by Embodiment 1 of the present invention is shown, and the implementation flow is described in detail as follows:

[0022] In step S101, the address information of the instruction data is acquired;

[0023] In the embodiment of the present invention, when the microcontroller reads the instruction data, it sends the address information of the instruction data to the cache to determine whether the instruction data has been cached in the cache.

[0024] In step S102, it is detected whether the address information of the instruction data exists in the static random access memory SRAM;

[0025] In the embodiment of the present invention, the SRAM is used to store the address information of the instruction data cached in the cache.

[0026] Exemplarily, a 4K-byte cache is used, 4K bytes are 1K words, if the cache caches 4 words at a time, it needs to store 256 address information, and one address ...

Embodiment 2

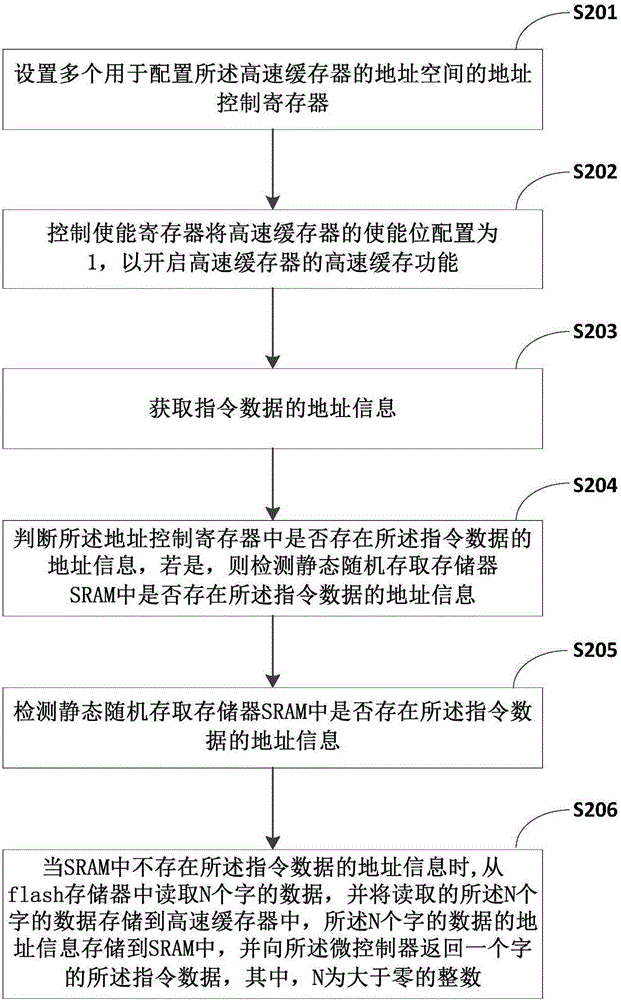

[0039] figure 2 The implementation flow of the microcontroller cache method provided by Embodiment 2 of the present invention is shown, and the implementation flow is described in detail as follows

[0040] In step S201, a plurality of address control registers for configuring the address space of the cache memory are set;

[0041] In the embodiment of the present invention, a plurality of address control registers are used to configure the address space of the cache memory, and the address information of the instruction data in the flash memory is allocated to the address space of the cache memory to determine whether the instruction data Caching is required. For example, if one of the address control registers configures the address space of the cache as 100-4ff, then any instruction data belonging to the address information in this address range can be cached.

[0042] In step S202, the control enable register configures the enable bit of the cache as 1 to enable the cach...

Embodiment 3

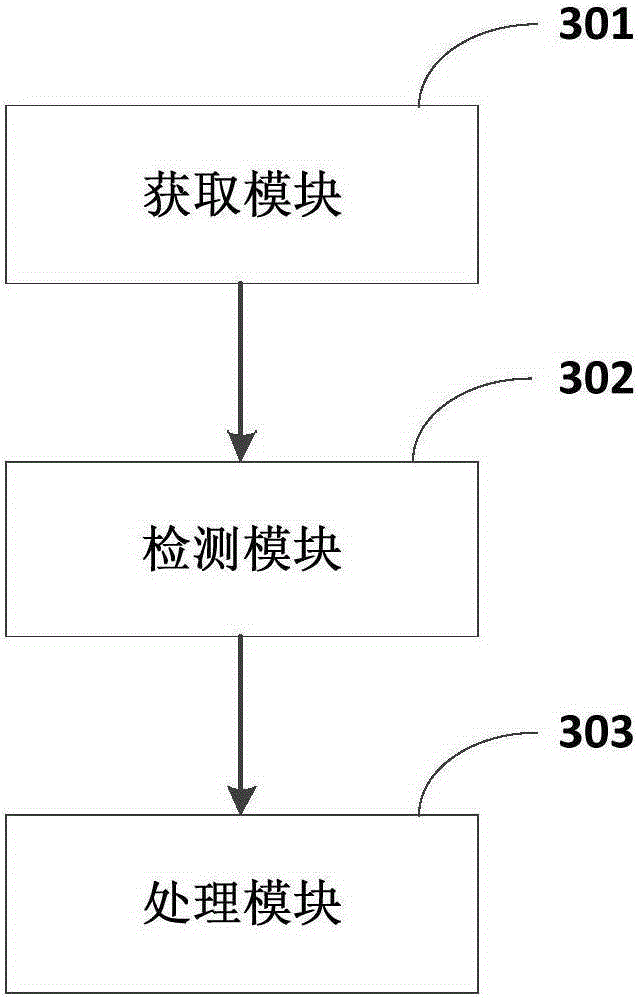

[0063] image 3 A schematic diagram of the composition of the microcontroller cache device provided by the third embodiment of the present invention is shown. For the convenience of description, only the parts related to the embodiment of the present invention are shown, and the details are as follows:

[0064] An acquisition module 301, configured to acquire address information of instruction data;

[0065] A detection module 302, configured to detect whether address information of the instruction data exists in the static random access memory SRAM;

[0066] The processing module 303 is used to read the data of N words from the flash memory when the address information of the instruction data does not exist in the SRAM, and store the data of the N words read into the cache memory wherein, the address information of the N words of data is stored in the SRAM, and one word of the instruction data is returned to the microcontroller, wherein, N is an integer greater than zero.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More