Method for forming semiconductor structure

A technology of semiconductor and dummy gate structure, applied in semiconductor/solid-state device manufacturing, electrical components, circuits, etc., can solve problems such as adverse effects of semiconductor devices

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

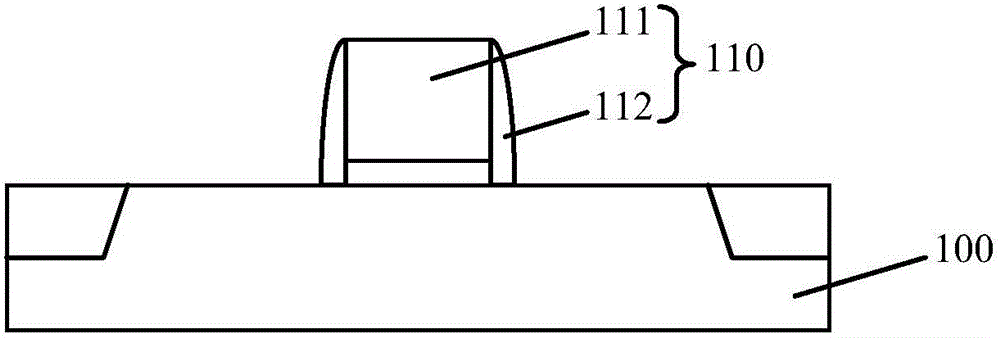

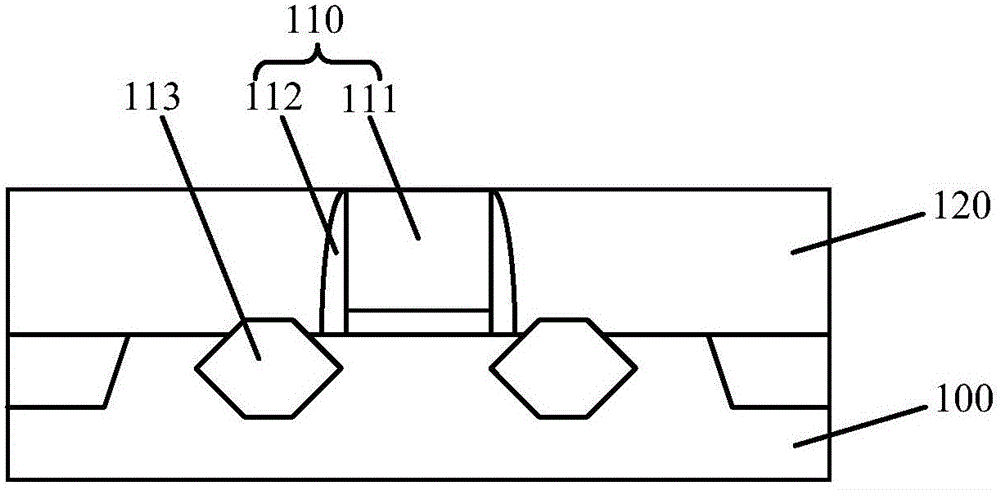

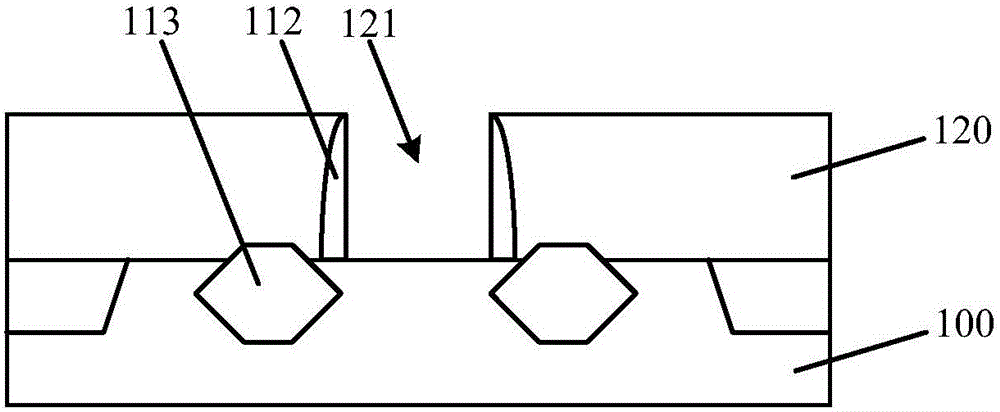

Embodiment Construction

[0033] As mentioned in the background, with the wide application of high-k dielectric materials, the disadvantages of high-k dielectric materials have more and more serious adverse effects on semiconductor devices.

[0034] After research, it is found that the atoms in the high-k dielectric material will be polarized under the action of an alternating electric field, and will return to an electrical equilibrium state through a relaxation process, that is, the phenomenon of relaxation (Dielectric Relaxation, DR for short). During the relaxation process, the polarized atoms in the high-k dielectric material need a certain relaxation time to return to an electrical equilibrium state, and during the relaxation process, a relaxation current is generated in the high-k dielectric material, resulting in energy loss. Specifically, the polarization intensity in the high-k dielectric material has a phase angle lagging behind the alternating electric field, and the energy loss caused by t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More