A Timing Design Method for Modulation Domain Measurement in Short Time Interval

A design method and modulation domain technology, applied in the field of short-time interval modulation domain measurement sequence design, can solve the problems of increasing measurement time, constraints, time errors, etc., and achieve the effects of improving efficiency, low cost, and simplifying timing

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0032] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

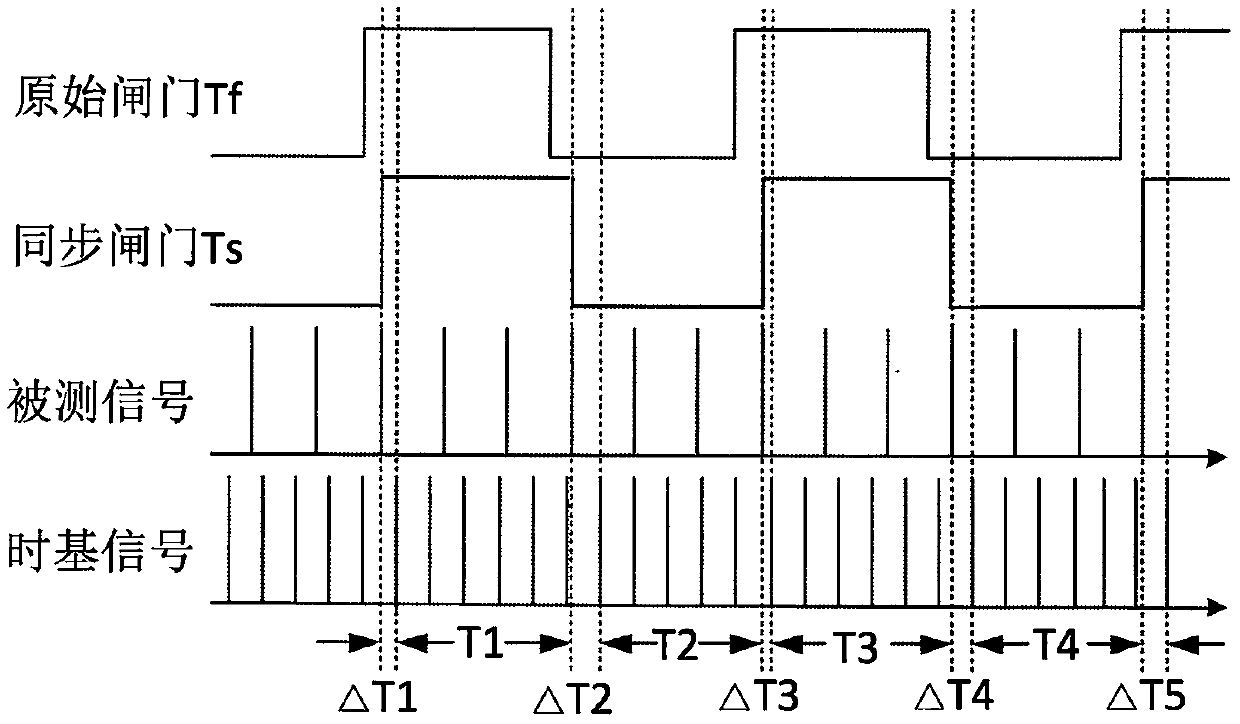

[0033] The time sequence processing of short time interval measurement in the prior art is limited by the size of the gate, and the time for one measurement is long and the efficiency is low.

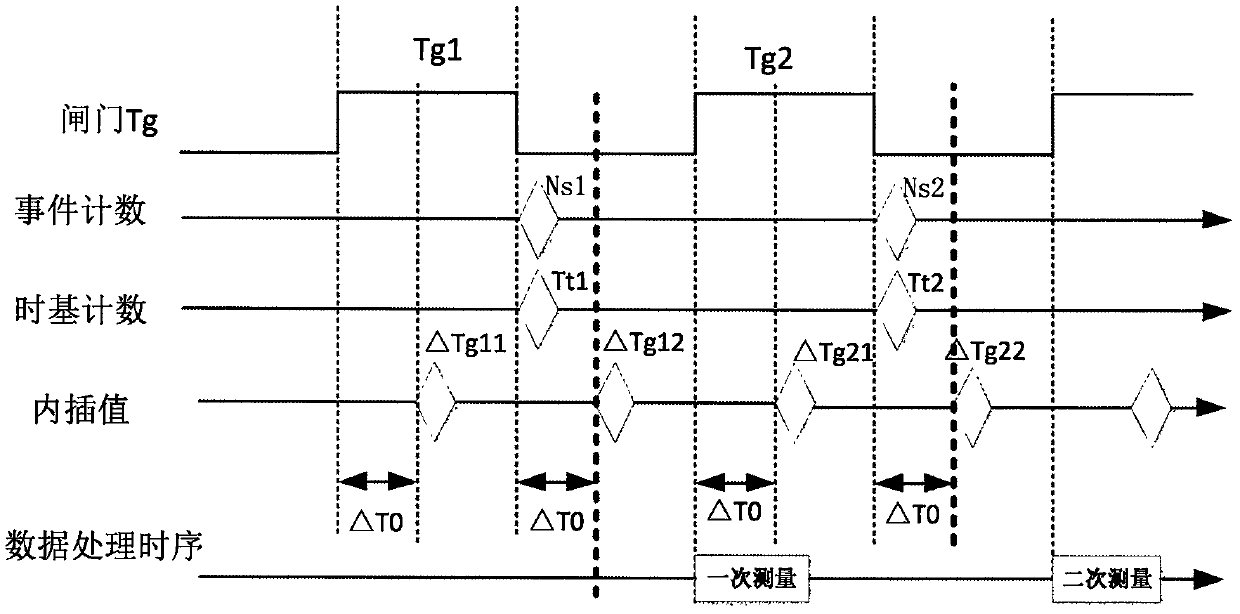

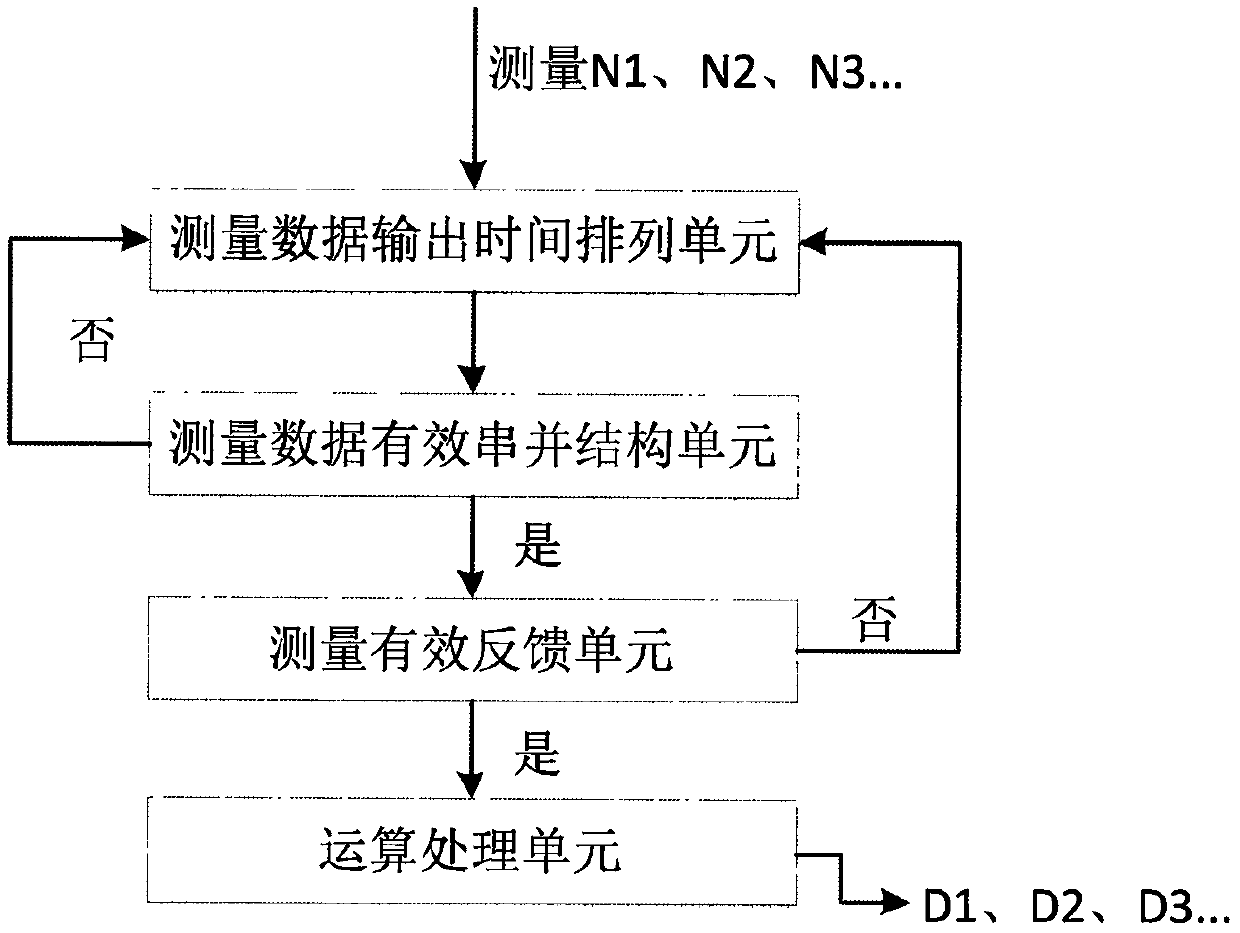

[0034] The present invention proposes an effective measurement data output feedback mechanism, abandons the traditional method of processing data during the high and low periods of the time gate, gets rid of the time limit of the gate, and further shortens the time inter...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More