FPGA (Field Programmable Gate Array) circuit and window signal adjustment method

A circuit and signal technology, applied in the field of FPGA circuit and window signal adjustment, can solve the problems of large adjustment range, low accuracy and efficiency, and achieve the effect of good matching and improving adjustment efficiency.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

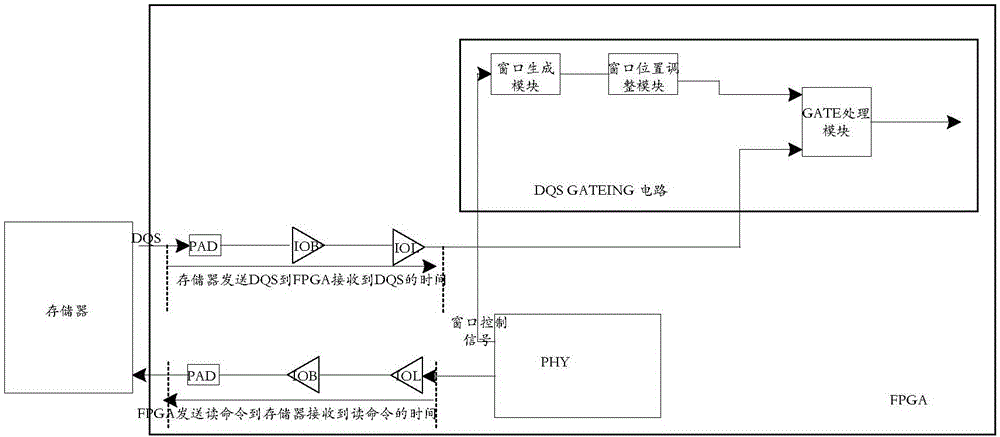

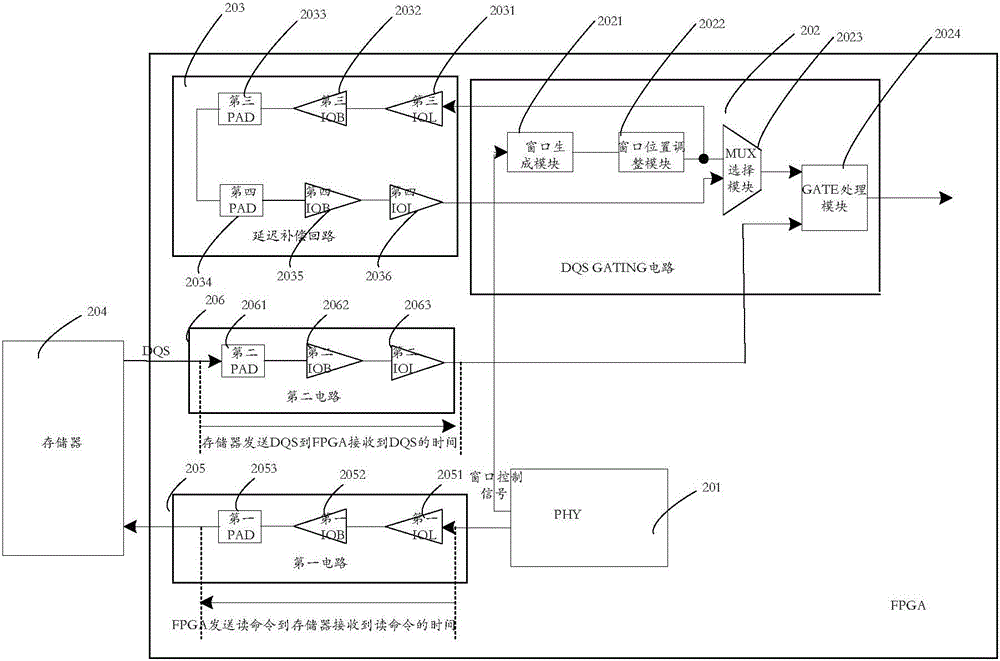

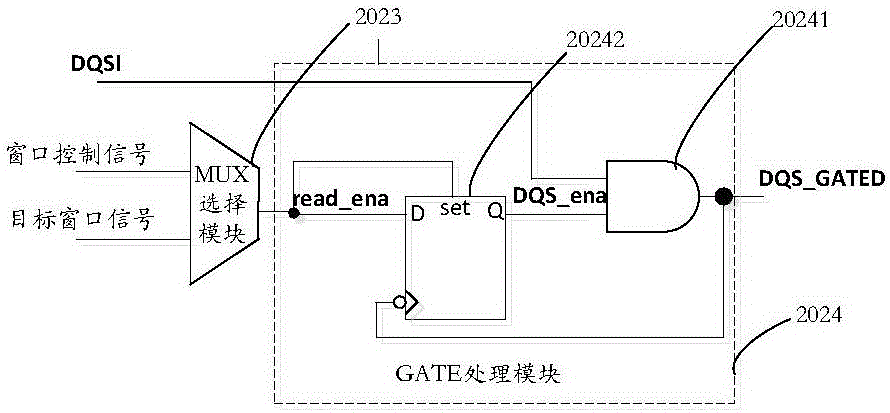

[0047] This embodiment provides a kind of FPGA circuit, see figure 2 , figure 2 The schematic diagram that a kind of FPGA circuit that this embodiment provides is connected with external memory; figure 2 Among them, the external memory 204 is connected with the FPGA circuit; the FPGA circuit includes:

[0048] PHY201, DQS GATING circuit 202 connected to PHY 201, delay compensation loop 203 connected to DQS GATING circuit 202, first circuit 205 connected between PHY201 and external memory 204, connected between external memory 204 and DQS GATING circuit 202 Between the second circuit 206; where,

[0049] Both ends of the delay compensation loop 203 are respectively connected to both ends of the DQS GATING circuit 202;

[0050] PHY201, used to send a read command to the external memory 204 through the first circuit 205, and at the same time send a window control signal to the DQS GATING circuit 202;

[0051] Optionally, the first circuit 205 includes a first IOL2051, a fi...

Embodiment 2

[0084] This embodiment provides a window signal adjustment method, which is applied to the FPGA circuit in Embodiment 1, PHY201, DQS GATING circuit 202 connected to PHY 201, delay compensation circuit 203 connected to DQS GATING circuit 202, connected between PHY201 and external The first circuit 205 between the memory 204, the second circuit 206 connected between the external memory 204 and the DQS GATING circuit 202; the two ends of the delay compensation loop 203 are respectively connected with the two ends of the DQS GATING circuit 202; see Figure 7 , Figure 7 It is a flowchart of a window signal adjustment method provided in this embodiment, and the window signal adjustment method includes the following steps:

[0085] S701: The PHY 201 sends a read command to the external memory 204 through the first circuit 205, and simultaneously sends a window control signal to the DQS GATING circuit 202;

[0086] Optionally, the first circuit 205 includes a first IOL2051, a first IO...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More