Transistor and forming method thereof

A transistor and U-shaped technology, applied in the field of transistors and their formation, can solve the problems of low mobility and inability to better improve the performance of semiconductor devices, so as to improve mobility, improve the barrier reduction effect introduced by the drain terminal, and reduce the tip The effect of discharge

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] It can be known from the background art that the transistor in the prior art has the problem of low carrier mobility in the channel region. Now combined with the structure of the transistor to analyze the reasons for the low carrier mobility:

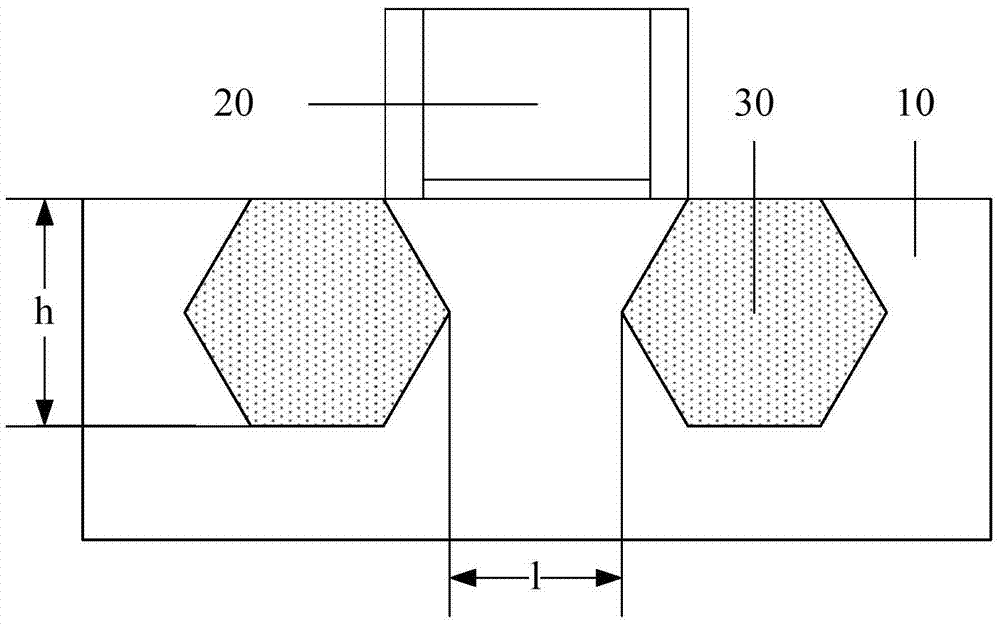

[0041] refer to figure 1 , showing a schematic diagram of the structure of a transistor.

[0042] The transistor includes: a substrate 10 and a gate structure 20 located on the surface of the substrate 10 .

[0043] In order to improve the carrier mobility in the transistor channel region, Sigma-shaped stress layers 30 are usually arranged in the substrate 10 on both sides of the gate structure 20 . The sigma-shaped stressor layer 30 has a bulge directed toward the channel region, and the stress material located at the bulge is closer to the channel region, which can induce greater stress in the channel region.

[0044] In order to enable the stressor layer 30 to introduce enough stress in the channel region, the stressor laye...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More