Multichip synchronization structure based on time-digital converter circuit

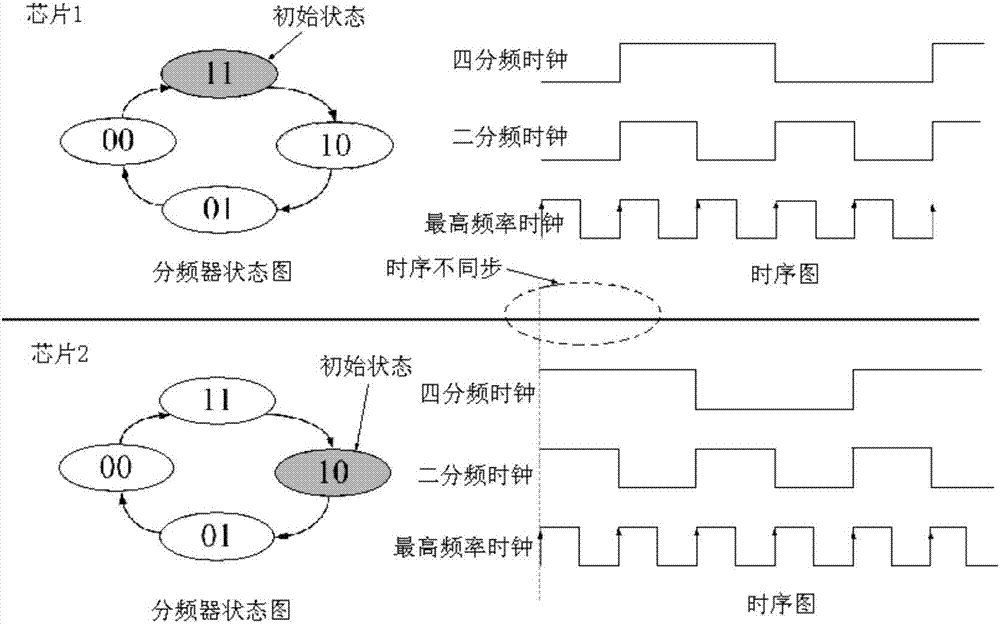

A digital converter, multi-chip technology, applied in electrical digital data processing, instrumentation, generation/distribution of signals, etc., can solve the timing deviation of the synchronization indication signal, the poor quality of the synchronization indication signal waveform, and the high requirements for the driving capability of the synchronization indication signal source. Advanced problems, to achieve the effect of improving reliability, reducing load, and eliminating transmission delay

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

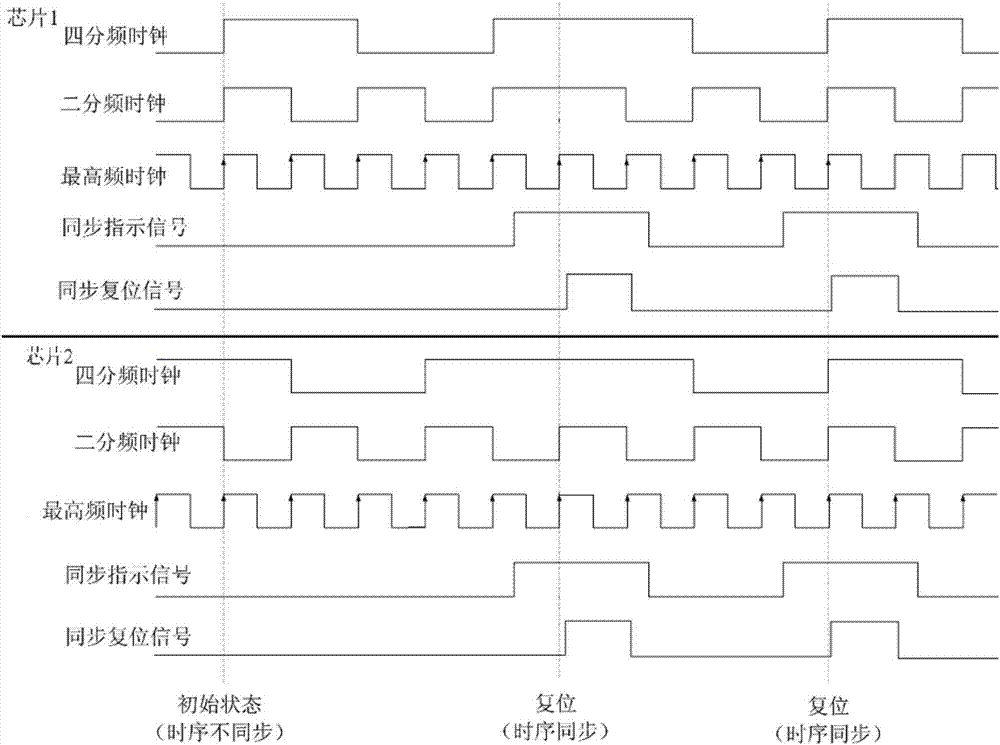

[0020] The preferred embodiments of the present invention will be described in detail below in conjunction with the accompanying drawings; it should be understood that the preferred embodiments are only for illustrating the present invention, rather than limiting the protection scope of the present invention.

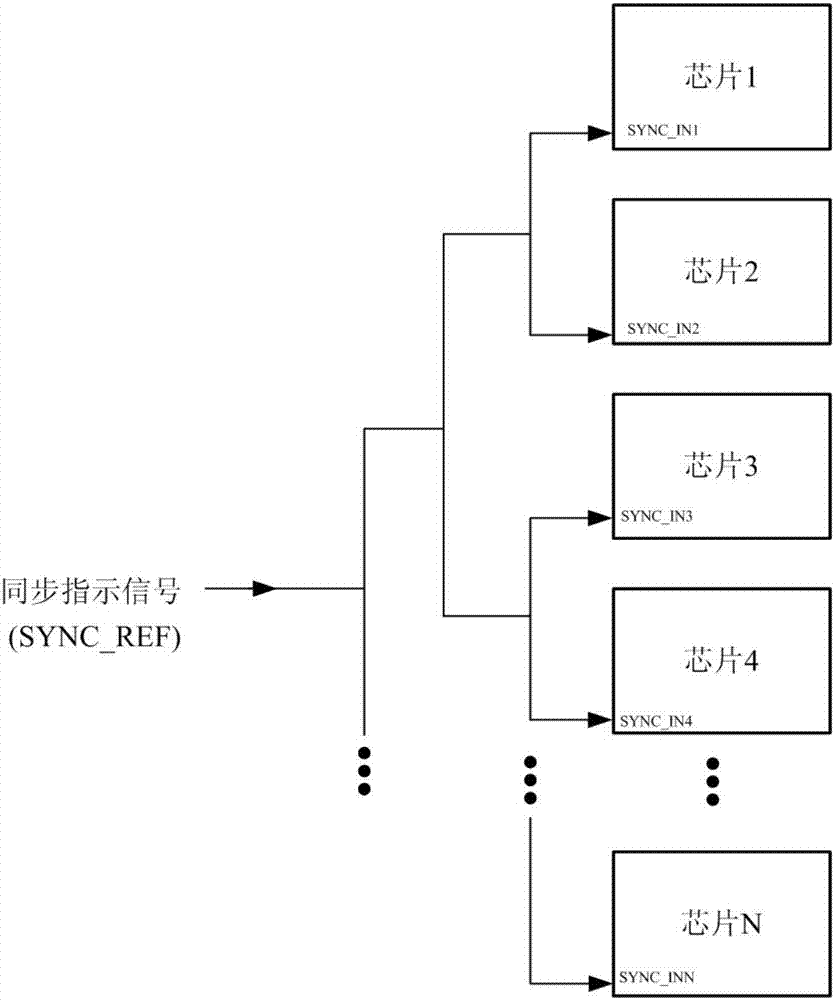

[0021] Such as Figure 4 As shown, a multi-chip synchronization structure based on a time-to-digital converter circuit includes N identical circuit chips with built-in time-to-digital converters and timing adjustment modules.

[0022] The following is an illustration with 3 chips.

[0023] The synchronization indication reference signal (SYNC_REF signal) provided by the whole system is connected to the SYNC_IN1 terminal of the chip 1 and the input terminal of the time-to-digital converter IN1 of the chip 1 . The SYNC_OUT1 terminal of chip 1 is connected to the SYNC_IN2 terminal of chip 2, the input terminal of the time-digital converter IN2 of chip 1 and the input term...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More