Simulation method for improving PCIE eye diagram margin

A simulation method and margin technology, applied in design optimization/simulation, special data processing applications, instruments, etc., can solve problems such as increased design cost, large crosstalk, and excessive crosstalk, so as to ensure integrity and reduce link Effect of Crosstalk Size

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0017] The simulation method of the present invention will be further described in detail in conjunction with specific embodiments below:

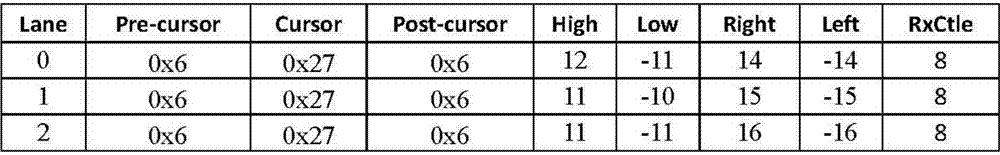

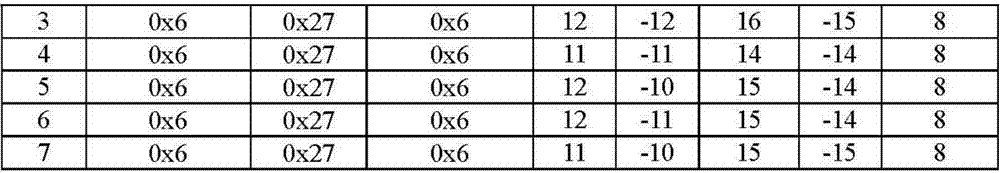

[0018] Through the simulation analysis of the link with short PCIE bus trace and large crosstalk on the main board, the judgment standard is that the margin must be greater than 9, and only when it is greater than 9 can the link signal integrity be guaranteed.

[0019] Among them, the TX end sets (Pre-cursor, Cursor, Post-cursor) sum 0x3F(63). Under this amplitude, even if preset0-9 traverses, the eye diagram (the eye diagram refers to the use of experimental methods to estimate and improve system performance) An observed graphic) margin is not ideal (High, low, right, and left represent the eye margin), the test results take (0x0b, 0x29, 0x0b) as an example, and the specific results are shown in Table 1.

[0020] Lane

Pre-cursor

Cursor

Post-cursor

High

Low

Right

Left

RxCtle

0

0x0b

0x2...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More