Verification method and verification system for interface controller

An interface controller and controller technology, applied in the field of interface controller verification method and verification system, can solve the problems of increasing verification workload and so on

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

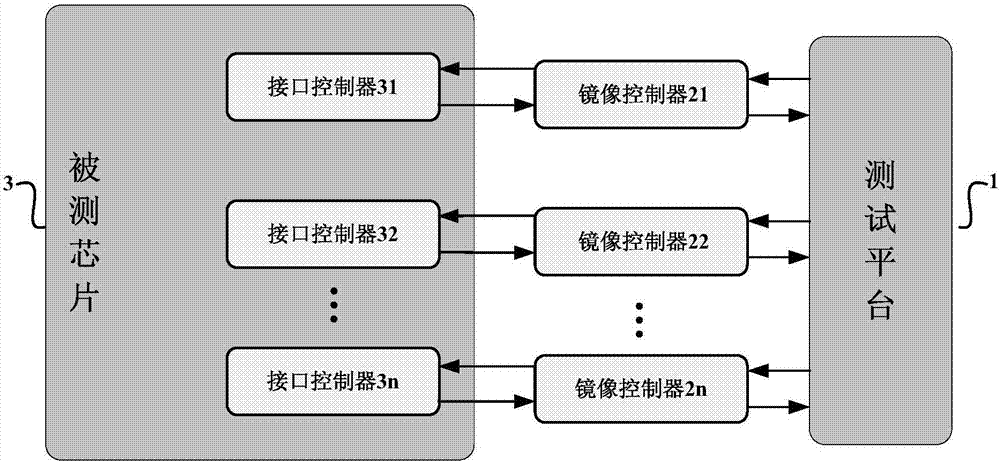

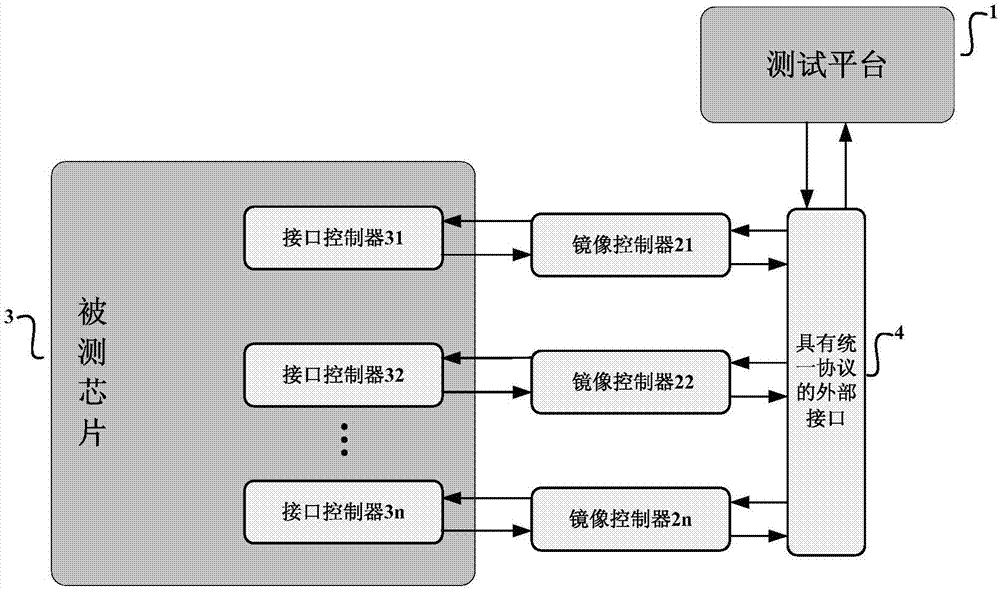

[0043] Such as Figure 2a Shown is a schematic structural diagram of a verification system for an interface controller provided by Embodiment 1 of the present invention, including: a test platform 1 and at least one mirror controller 2i (i is between 1 and n), each mirror controller 2i It is configured according to the type of interface controller 3i included in the chip under test 3, and the mirror controller 2i is connected to the interface controller 3i of the same type, and the mirror controller is also connected to the test platform 1, wherein:

[0044] The test platform 1 is used to generate initial test data when verifying any interface controller 3i (i is between 1 and n) in the tested chip 3, and use simple The driver sends to the mirror controller 2i corresponding to the interface controller 3i; and receives the fourth test data returned by the mirror controller 2i; compares the initial test data with the fourth test data; and according to the comparison result, Determi...

Embodiment 2

[0083] Such as Figure 5 As shown, it is a schematic flowchart of a verification method for a test platform-side interface controller provided in the second embodiment of the present invention, which may include the following steps:

[0084] S11. Generate initial test data when verifying any interface controller in the tested chip.

[0085] S12. Send the initial test data to the mirror controller corresponding to the interface controller using a simple driver.

[0086] During specific implementation, when the initial test data is sent to the mirror controller, the mirror controller can be triggered to perform data format conversion on the received initial test data to obtain the first test data, and the The test data is sent to the mirror controller corresponding to the interface controller.

[0087] S13. Receive fourth test data returned by the mirror controller.

[0088] Wherein, the fourth test data is obtained by the mirror controller performing data format conversion processing on...

Embodiment 3

[0101] Such as Image 6 As shown, it is a schematic flowchart of a method for verifying a mirror controller-side interface controller provided in Embodiment 3 of the present invention, which may include the following steps:

[0102] S21: After receiving the initial test data sent by the test platform using a simple driver, perform data format conversion on the initial test data to obtain the first test data.

[0103] Wherein, the initial test data is generated when the test platform verifies any interface controller in the chip under test.

[0104] S22. Send the first test data to the chip under test.

[0105] S23. Receive third test data sent by the chip under test, and perform data format conversion processing on the third test data to obtain fourth test data.

[0106] Wherein, the third test data is obtained by performing data format conversion on the second test data by the chip under test again, and the second test data is obtained by performing the data format inverse of the chip ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More