Manufacturing method of super small unit size vertical super-junction semiconductor device

A technology of superjunction semiconductor and manufacturing method, applied in semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve problems such as limited process limit capability of P-pillar width, inability to further reduce, and process scheme unable to meet requirements, etc.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

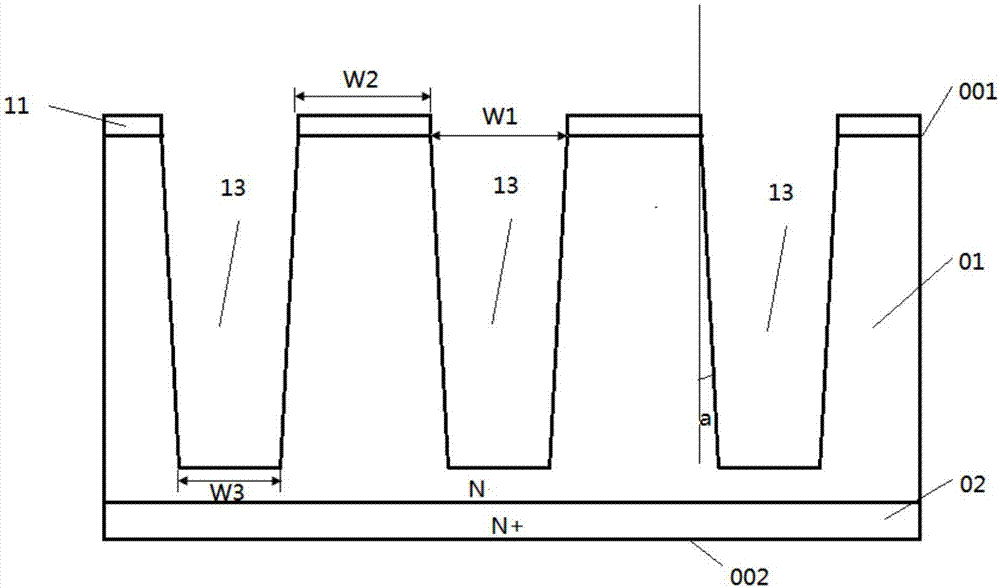

[0031] The present invention will be further described below by taking an N-type trench gate vertical super-junction MOSFET as an example and referring to specific drawings and embodiments. For an N-type super-junction semiconductor device, the first conductivity type is N-type, and the second conductivity type is P-type conductivity; for a P-type super-junction semiconductor device, the first conductivity type is P-type.

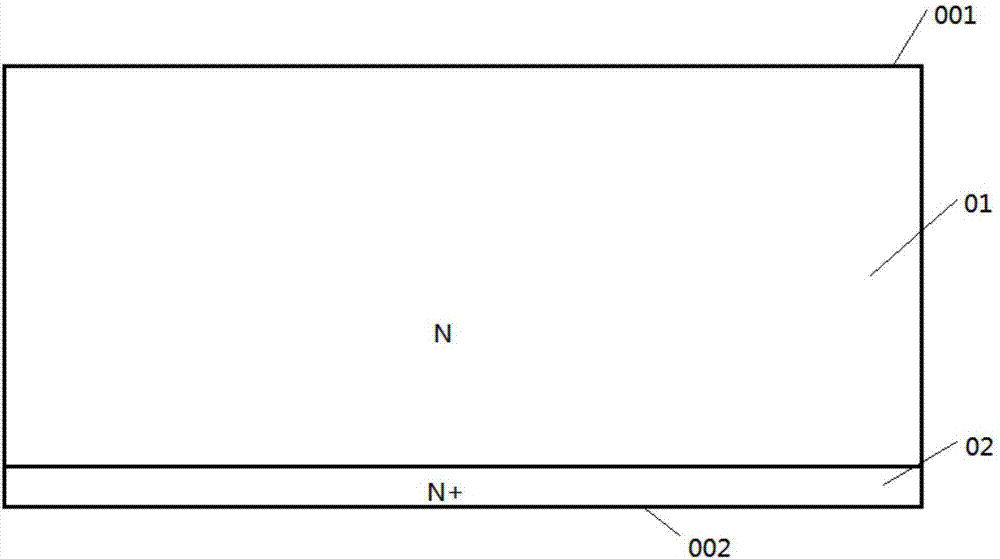

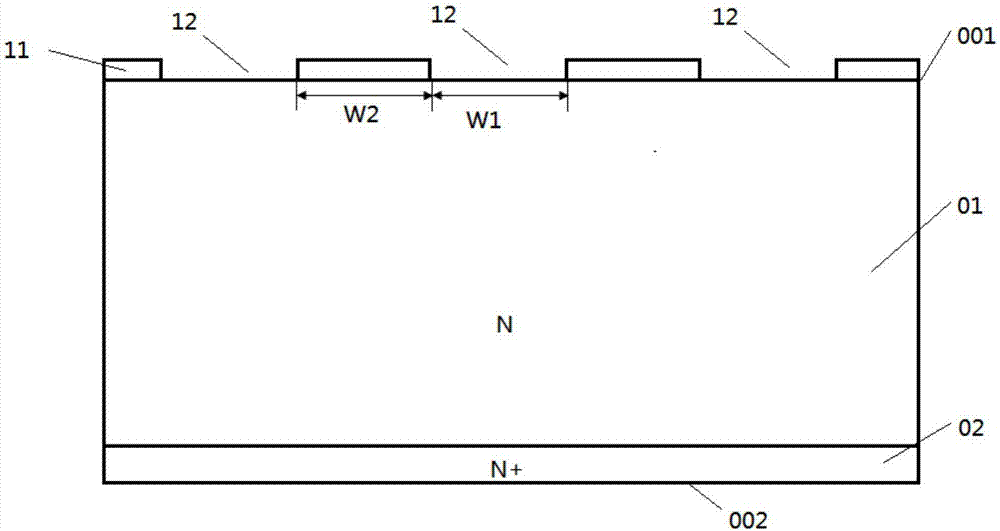

[0032] Such as Figure 8As shown, the ultra-small cell size vertical superjunction semiconductor device includes a semiconductor substrate, and the semiconductor substrate is an N-type semiconductor substrate having a first main surface 001 and a second main surface 002 corresponding to the first main surface 001; The N-type semiconductor substrate is composed of an N-type drift layer 01 including a first main surface 001 and an N+-type substrate 02 including a second main surface 002; the N-type drift layer 01 is provided with a plurality of deep grooves, ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More