Optimization of floating point complex vector summation based on BWDSP chips

A floating-point complex number and optimization method technology, applied in the direction of electrical digital data processing, program control design, instruments, etc., can solve the problems of inconvenient hardware system direct control, not combining the hardware characteristics of DSP chips, and not being able to play DSP chips, etc., to eliminate Pause, reduce the number of executions, and improve efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0034] The following will clearly and completely describe the technical solutions in the embodiments of the present invention with reference to the accompanying drawings in the embodiments of the present invention. Obviously, the described embodiments are only some, not all, embodiments of the present invention. Based on the embodiments of the present invention, all other embodiments obtained by persons of ordinary skill in the art without making creative efforts belong to the protection scope of the present invention.

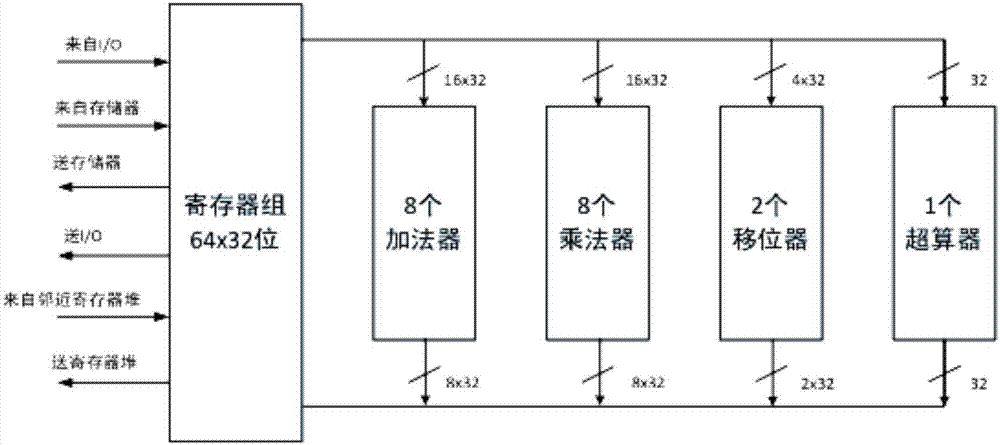

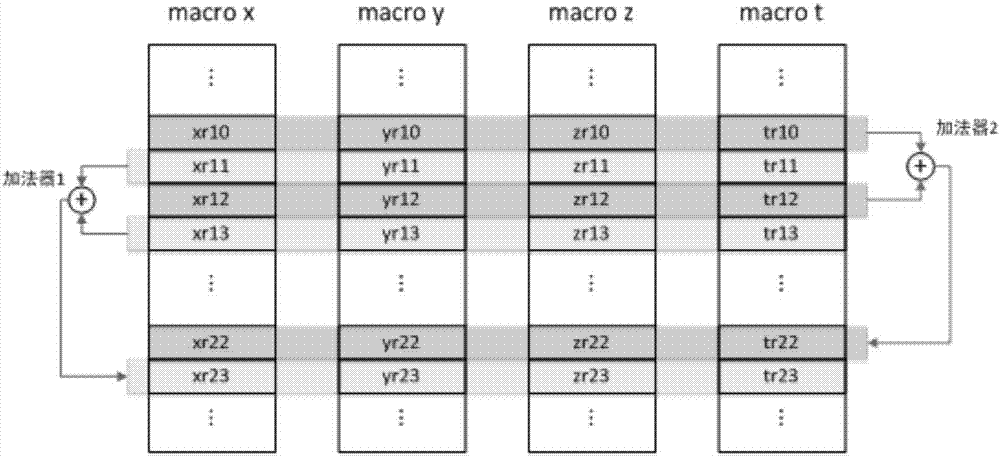

[0035] The development of low-level functions mainly uses the resources in the execution macros. The execution components of the processor are contained in four execution macros, which are called macro x, macro y, macro z, and macro t. The external interfaces and internal structures of the four execution macros are exactly the same. They obtain operation commands from the decoder, obtain operands from the data memory, and perform various specific operations.

...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More