A multi-chip integrated packaging method

A packaging method and multi-chip technology, applied in the manufacturing of electrical components, circuits, semiconductor/solid-state devices, etc., can solve the problems of long trial production cycle, high design cost, and inability to meet time requirements, so as to reduce design costs and reduce costs. The effect of design link and shortening production cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

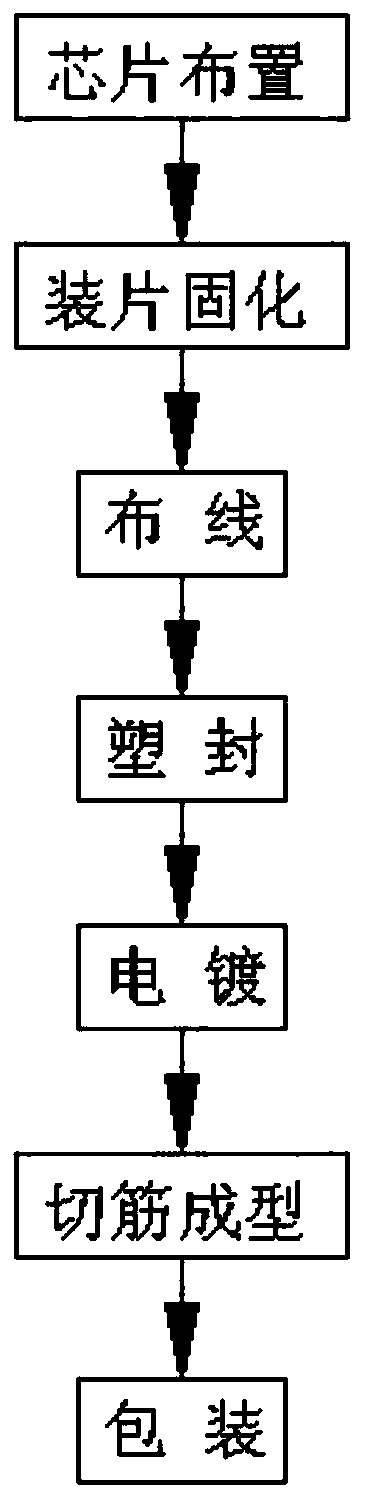

[0017] Such as figure 1 Shown, a kind of multi-chip integrated packaging method, this method comprises the following steps:

[0018] 1) Chip layout: according to the function and size of multiple functional chips, the chip layout method is determined, and the chip layout method is one or more combinations of horizontal layout in the horizontal direction and stacking layout in the vertical direction;

[0019] 2) Loading and curing: According to the chip arrangement method selected in step 1), each functional chip is loaded in sequence until all the functional chips are loaded and sent to an oven for baking and curing. The drying temperature of the oven is 175 ℃, the drying time is 2.5h;

[0020] 3) Wiring: Place the functional chip after loading and curing in step 2) on the upper end of the bonding heating platform, and automatically plant the ball on the functional chip. Make a reverse slicing platform on the top surface, and use bonding wire to interconnect the reverse slic...

Embodiment 2

[0027] Such as figure 1 Shown, a kind of multi-chip integrated packaging method, this method comprises the following steps:

[0028] 1) Chip layout: according to the function and size of multiple functional chips, the chip layout method is determined, and the chip layout method is one or more combinations of horizontal layout in the horizontal direction and stacking layout in the vertical direction;

[0029] 2) Loading and curing: According to the chip arrangement method selected in step 1), each functional chip is loaded in sequence until all the functional chips are loaded and sent to an oven for baking and curing. The drying temperature of the oven is 173 ℃, the drying time is 2.5h;

[0030] 3) Wiring: Place the functional chip after loading and curing in step 2) on the upper end of the bonding heating platform, and automatically plant the ball on the functional chip. Make a reverse slicing platform on the top surface, and use bonding wire to interconnect the reverse slic...

Embodiment 3

[0037] Such as figure 1 Shown, a kind of multi-chip integrated packaging method, this method comprises the following steps:

[0038] 1) Chip layout: according to the function and size of multiple functional chips, the chip layout method is determined, and the chip layout method is one or more combinations of horizontal layout in the horizontal direction and stacking layout in the vertical direction;

[0039] 2) Loading and curing: According to the chip arrangement method selected in step 1), each functional chip is loaded in turn until all the functional chips are loaded and sent to an oven for baking and curing. The drying temperature of the oven is 174 ℃, the drying time is 2.5h;

[0040] 3) Wiring: Place the functional chip after loading and curing in step 2) on the upper end of the bonding heating platform, and automatically plant the ball on the functional chip. Make a reverse slicing platform on the top surface, and use bonding wire to interconnect the reverse slicing ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More