Implementation method for BMC (Baseboard Management Controller) system lower-layer interface based on SoC (System on a Chip) FPGA (Field Programmable Gate Array)

A low-level interface and implementation method technology, applied in the server field, can solve the problems of large investment and long cycle of BMC management chip, etc., and achieve the effect of less manpower investment and short development cycle

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0045] The content of the present invention is described in more detail below:

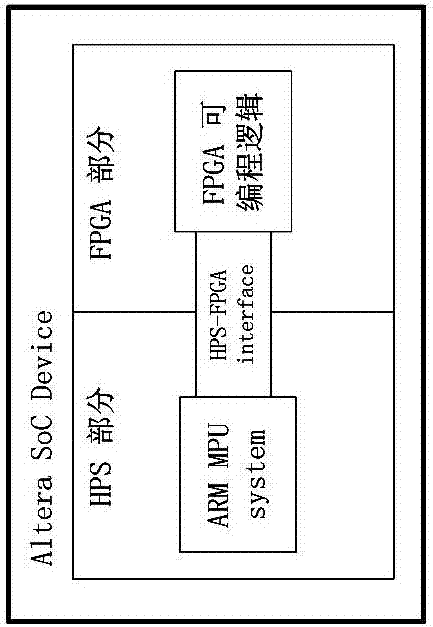

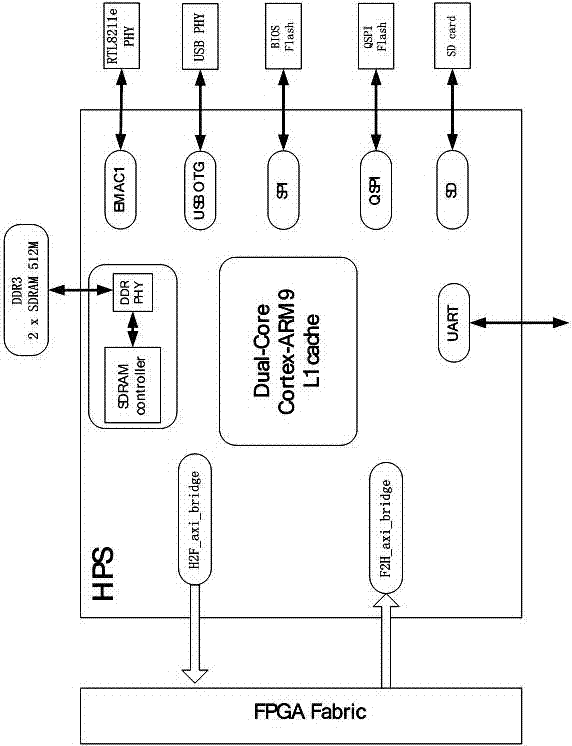

[0046] figure 1 It is a schematic diagram of the internal structure of Cyclone V series chips. This series of chips is divided into two parts: FPGA and HPS. The FPGA side is programmable logic with great flexibility. The HPS side contains two ARMs and various The integrated interface provides configuration parameters of various interfaces, which is highly integrated and easy to operate. The two communicate through the AXI bridge, which ensures the normal communication of the two parts.

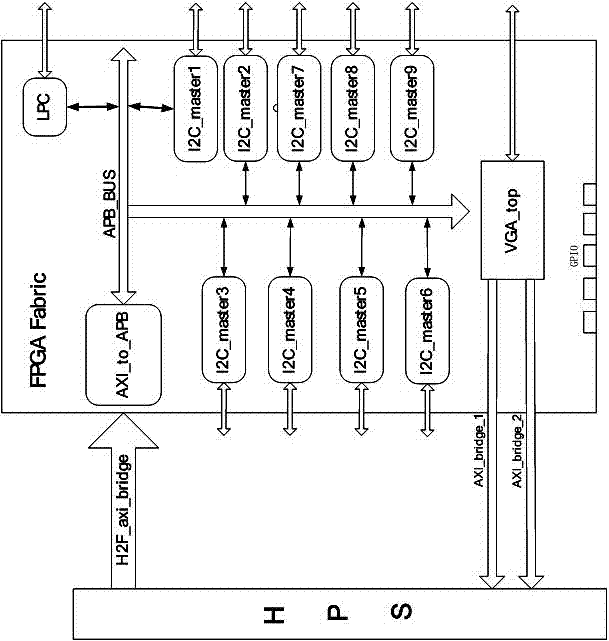

[0047] The bottom interface of the BMC management system implemented in the present invention can realize the following functions with software: provide rich management interfaces to meet the needs of system integration in various ways; meet the IPMI protocol and provide standard management interfaces; fault monitoring and diagnosis, early detection And solve problems; with virtual KVM and virtual media function...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com