Scribing groove test structure and test method thereof

A technology of test structure and test method, applied in the direction of semiconductor/solid-state device test/measurement, electrical components, electrical solid-state devices, etc., can solve the problems that the dicing groove cannot be further narrowed, restrict the integration of chips, etc., and achieve significant technical effects , improve the effect of integration

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

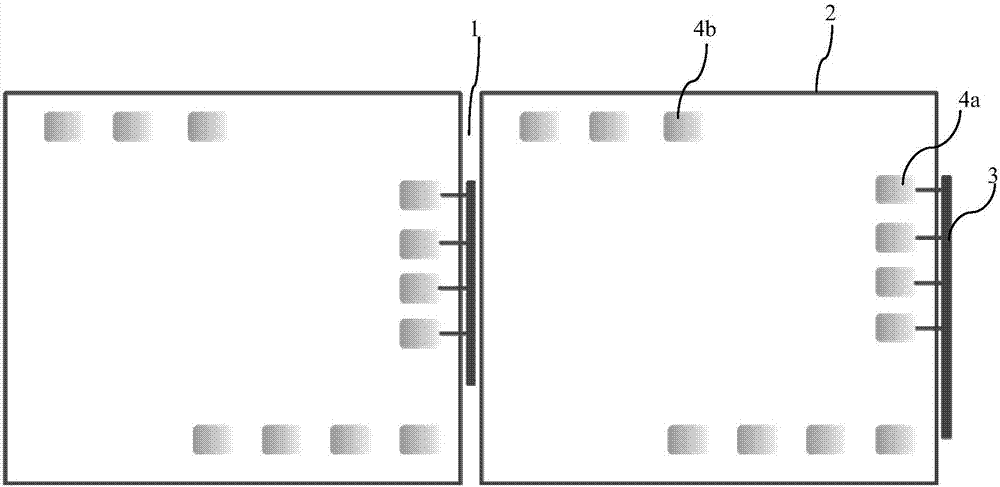

[0028] Such as figure 1 As shown, it is a schematic diagram of the scribe groove test structure of the embodiment of the present invention. In the scribe groove test structure of the embodiment of the present invention, the chip formation area 2 and the scribe groove 1 are included on the same wafer. figure 1 Only two chip formation regions 2 are shown in , but actually there are chip formation regions 2 on the same wafer, and the higher the chip integration degree, the more chip formation regions 2 are.

[0029] The test structure 3 is formed in the scribe groove 1 .

[0030] The first pad 4a of the test structure 3 is formed in the chip formation area 2 and formed by patterning the top front metal layer.

[0031] The test structure 3 is connected to the first pad 4a through more than one front metal layer and corresponding contact holes.

[0032] Depend on figure 1 As shown, since the first pad 4a no longer covers the scribe groove 1 in the embodiment of the present inven...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Size | aaaaa | aaaaa |

| Side length | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More - Generate Ideas

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com