Method for establishing transistor noise model capable of scaling along with offset

A noise model and establishment method technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve time-consuming, cumbersome and complex problems, achieve simplified extraction process, simplified modeling process, and intuitive parameter results Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0019] In order to solve the complicated and time-consuming technical problems in the method for establishing a transistor noise model in the prior art, the present invention further provides a method for establishing a transistor noise model that scales with bias.

[0020] In order to solve the above technical problems, the above technical solutions will be described in detail below with reference to the accompanying drawings and specific embodiments.

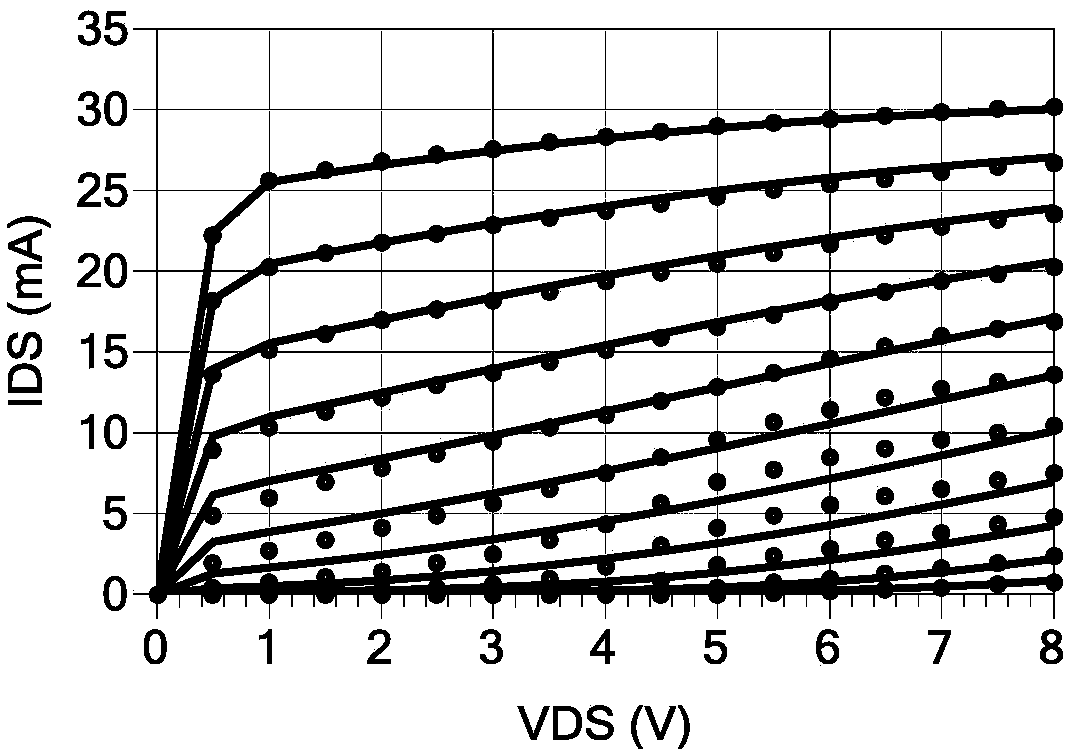

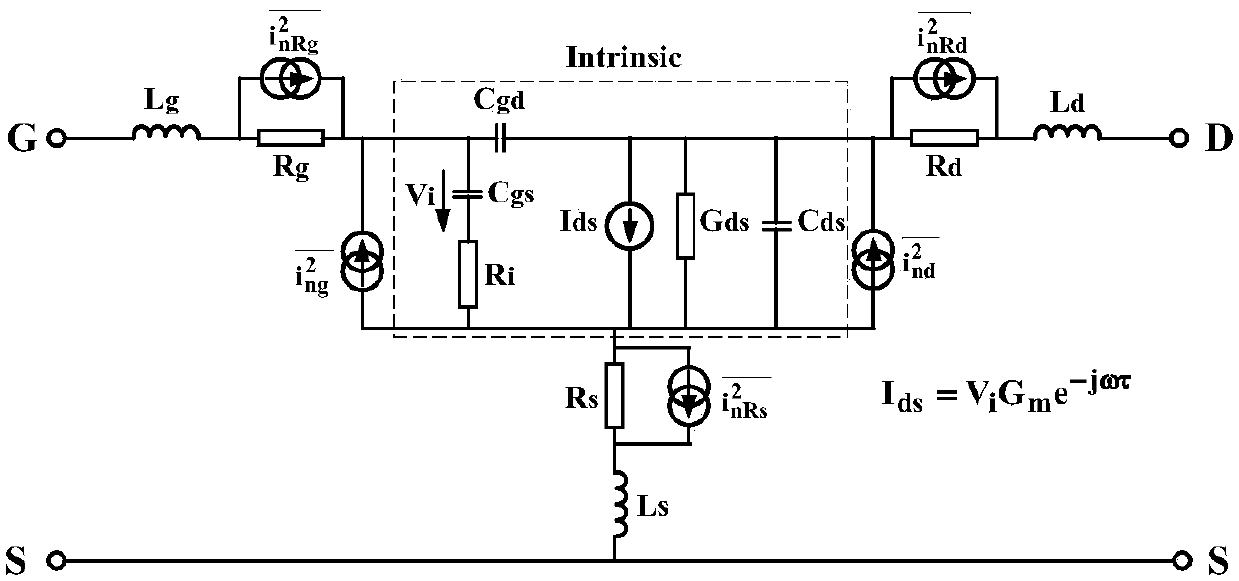

[0021] The present invention provides a method for establishing a transistor noise model scaled with bias, such as figure 1 shown, including: S101, measuring the DC IV characteristics of the transistor, selecting a DC IV model, and using the DC IV model to fit the tested DC IV data to obtain an accurate DC IV model; S102, based on the accurate DC IV model model, calculate the small-signal model parameters of the transistor, and obtain the small-signal model of the transistor; S103, based on the accurate DC IV model, obtain the...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More