A device for realizing clock and reset control chip working mode

A working mode and reset control technology, which is applied in the direction of logic circuit connection/interface layout, etc., can solve the problem that it is impossible to add an external pin PAD_IO, etc., and achieve the effect of ensuring safety certification, good compatibility, and easy transplantation

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

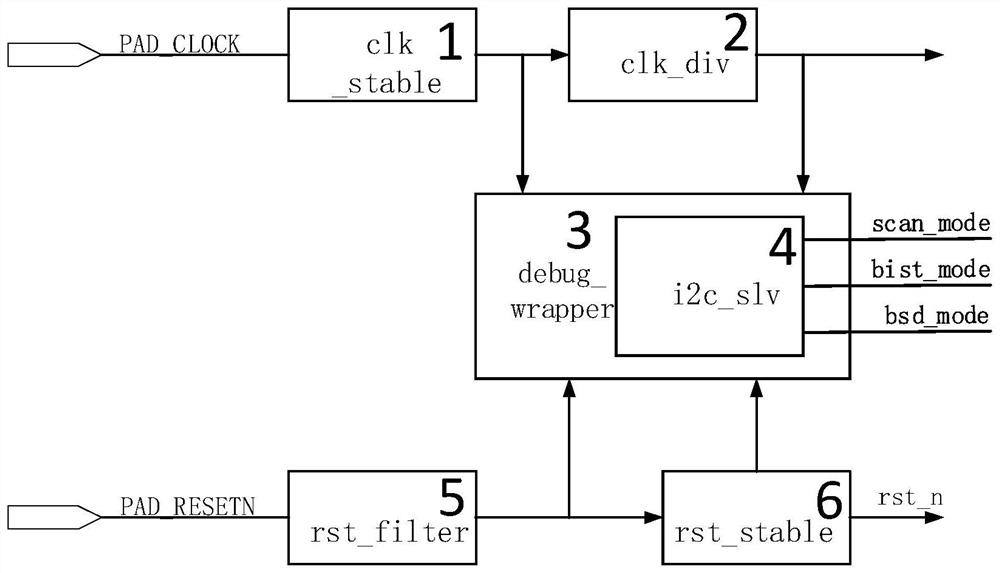

[0028] Attached below figure 1 , the specific embodiment of the present invention will be further described in detail.

[0029] It is clear to those skilled in the art that almost all digital circuit chips have clock PAD_CLOCK input pins and reset PAD_RESETN control pins, and the present invention only uses clocks and resets to control the chip operating mode (i.e. the selection of general operating mode and / or DFT operating mode) Switching) will not increase the associated costs, nor will it affect compatibility.

[0030] see figure 1 , figure 1 Shown is a block diagram of a device for realizing the working mode of the clock and reset control chip of the present invention. As shown in the figure, in addition to using the clock PAD_CLOCK input pin and the reset PAD_RESETN control pin, the implementation device also includes a clock stabilization circuit module clk_stable 1, a frequency division module clk_div 2, a filter circuit rst_filter 5, a debug controller debug_wrappe...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More