FC chip system stacked fan-out package structure and preparation method thereof

A packaging structure and chip system technology, which is applied in semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, semiconductor devices, etc., can solve the problems that multiple FC chips cannot be stacked, cannot meet industrial needs, and limit system integration. , to achieve the effects of improving packaging efficiency, simplifying interconnection methods, and simplifying the process

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0031] The present invention will be further described below in conjunction with specific drawings and embodiments.

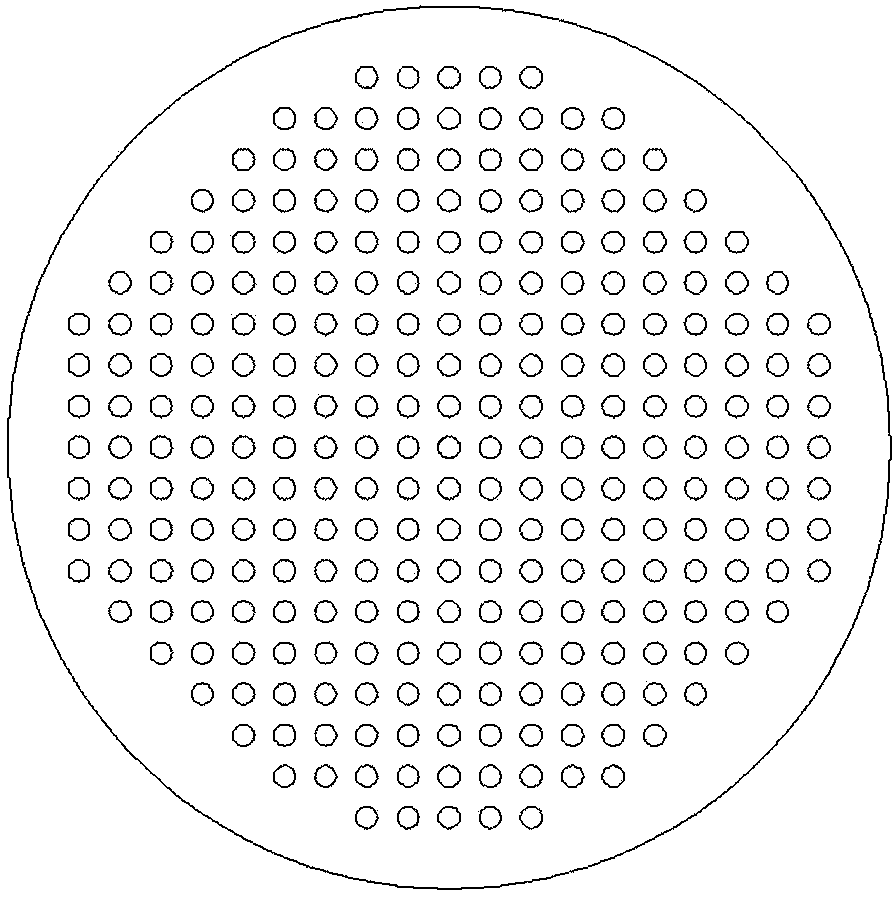

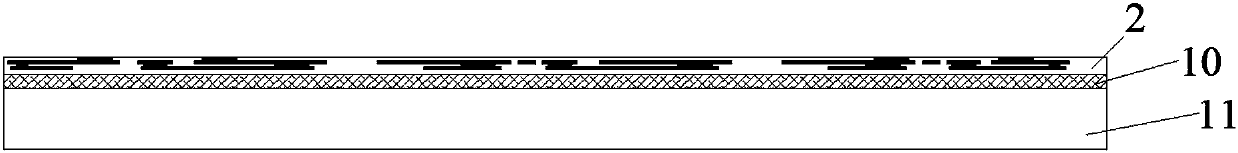

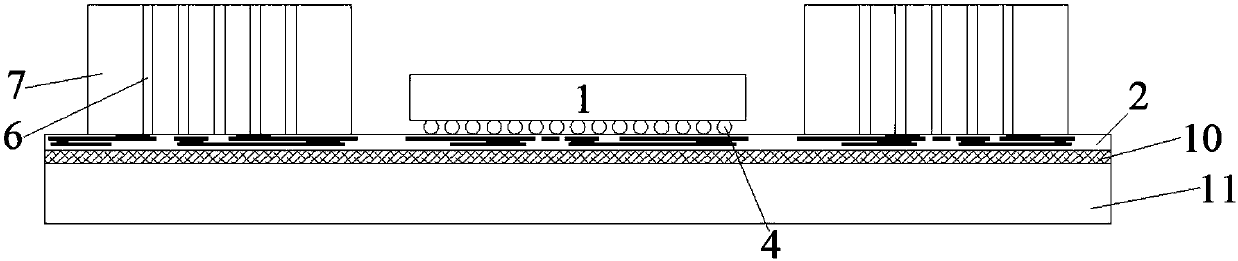

[0032] Such as Figure 7 As shown: in order to effectively realize the stack packaging of FC chips, the present invention includes a stack package formed by two FC chips 1, and the backs of the two FC chips 1 in the stack package are in contact with each other; The rewiring layer 2, the lower rewiring layer 3 is arranged under the stacked package, and the corresponding chip bumps 4 of the two FC chips 1 in the stacked package are respectively electrically connected to the upper rewiring layer 2 and the lower rewiring layer 3;

[0033] A symmetrically distributed vertical interconnection adapter board 7 is arranged on the outside of the stacked package, and the required connection between the upper rewiring layer 2 and the lower rewiring layer 3 is performed through the through-hole connectors 6 in the vertical interconnection adapter board 7 respectively. elec...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More