A time amplifier and a semiconductor memory

A time amplifier, the technology of the first time, applied in the direction of amplification control, electrical components, gain control, etc., can solve the problems of low measurement accuracy, time amplification gain can not be adjusted according to actual needs, etc., to achieve adjustable gain, The effect of increasing the amplification gain

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

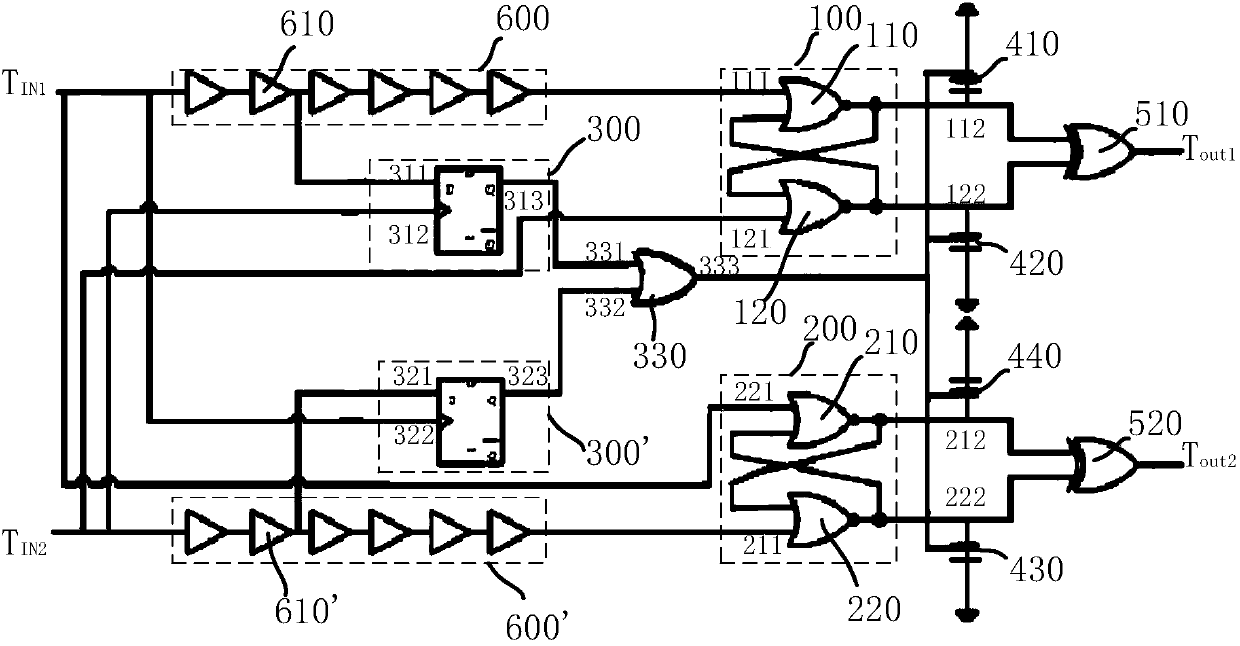

[0062] In a specific implementation, a time amplifier is provided, including:

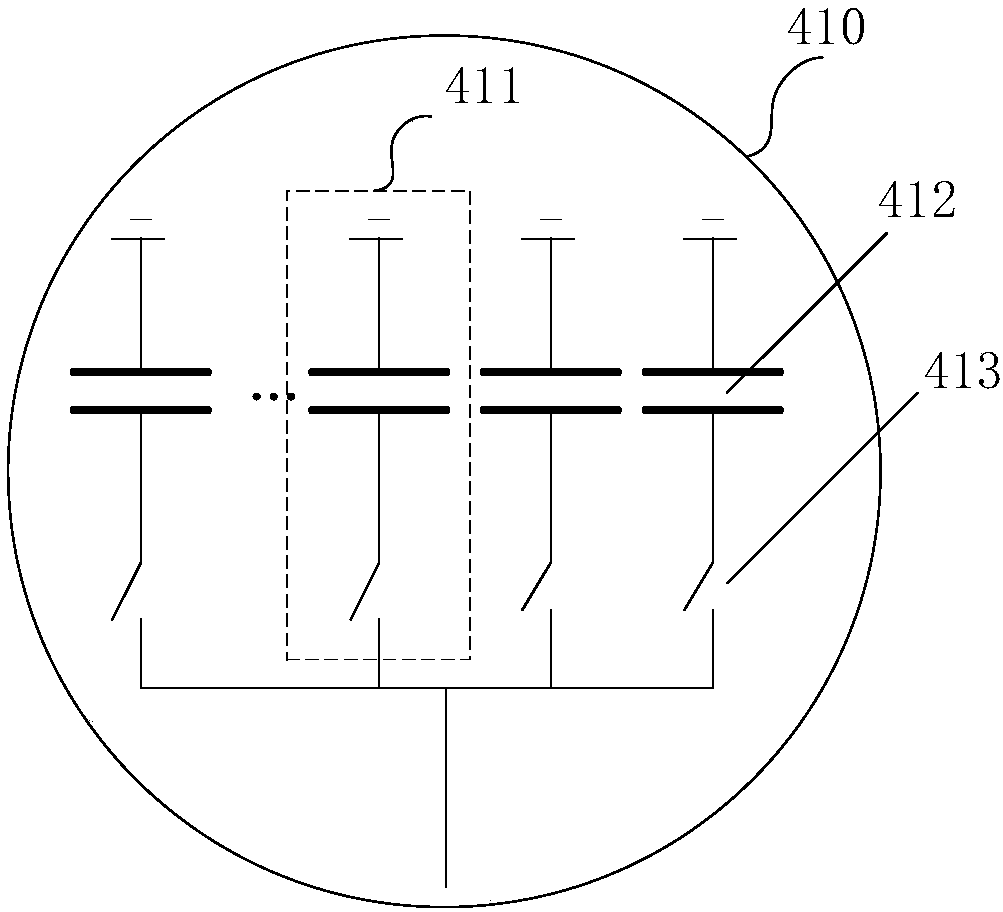

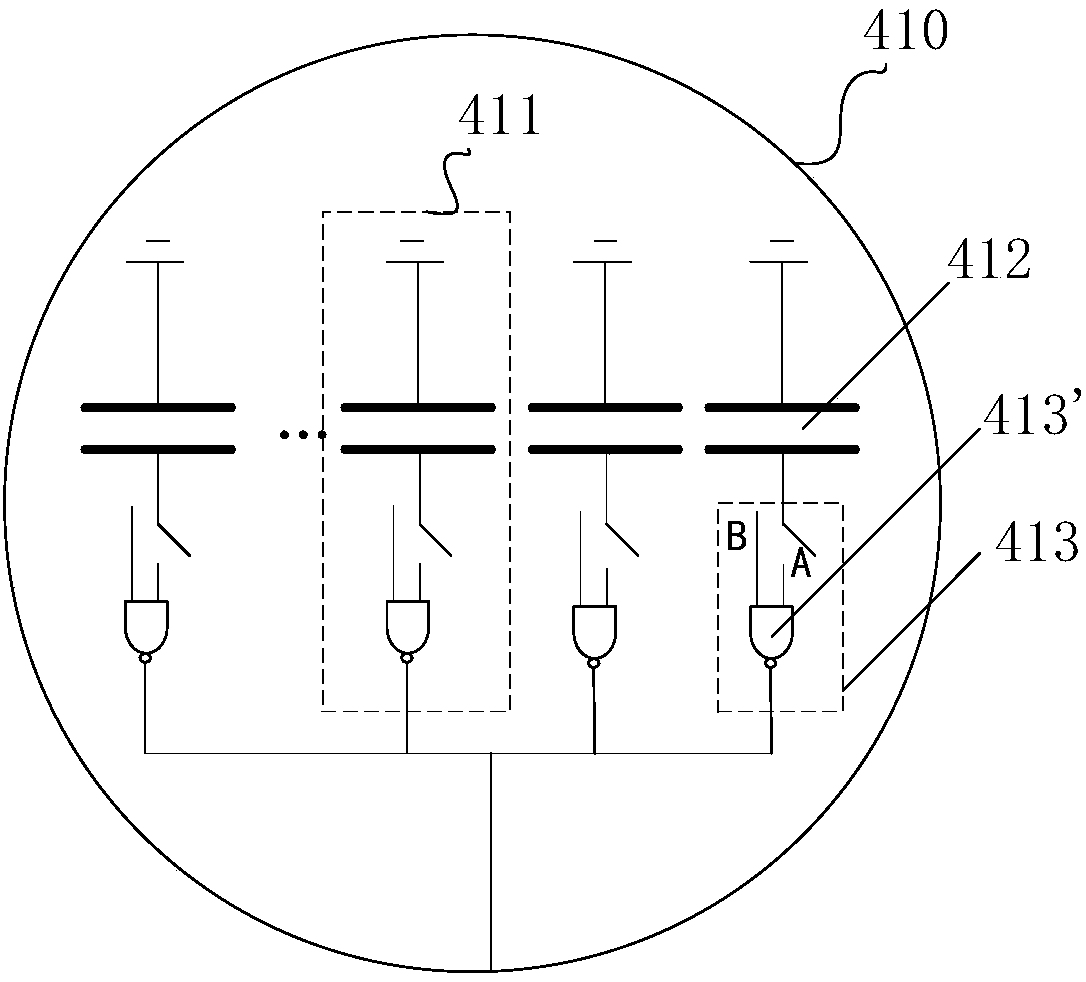

[0063] The first latch 100, the first buffer 600, the first buffer 600 is used to receive the first time pulse T IN1 The first latch input 111 of the first latch is connected to the output of the first buffer 600, and the second latch input 121 of the first latch receives the second time pulse T IN2 , the Q output terminal 112 of the first latch is coupled with a first capacitor 410, the first latch The output terminal 122 is coupled with a second capacitor 420;

[0064] The first D flip-flop 300, the first trigger input terminal 311 of the first D flip-flop receives from the first buffer 600 the first time pulse T delayed by a predetermined time interval IN1 , the second trigger input 312 of the first D flip-flop receives the second time pulse T IN2 , the first trigger output terminal 313 of the first D flip-flop is connected to at least one of the first capacitor 410 and the second capacitor ...

Embodiment 2

[0083] In another specific implementation manner, a semiconductor memory is also provided, including the time amplifier described in any one of the above.

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More