Variable cycle capacitor establishment asynchronous time sequence optimization circuit and optimization method

An asynchronous timing and variable technology, applied in multi-objective optimization, CAD circuit design, electrical digital data processing, etc., can solve the problems of limited cycle waste, low-bit capacitor allocation and redundant setup time, etc., to improve robustness and increase power Consumption and design difficulty, avoiding the effect of redundant waiting time

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0018] The present invention will be described in further detail below in conjunction with the accompanying drawings.

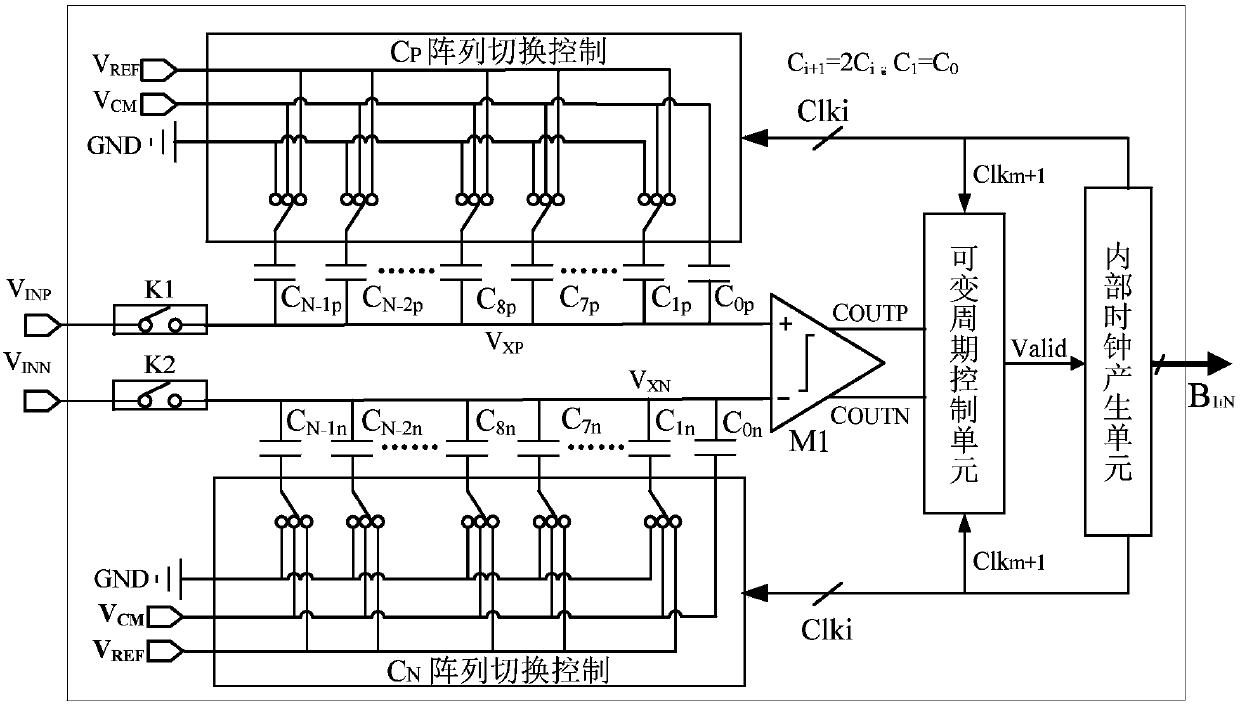

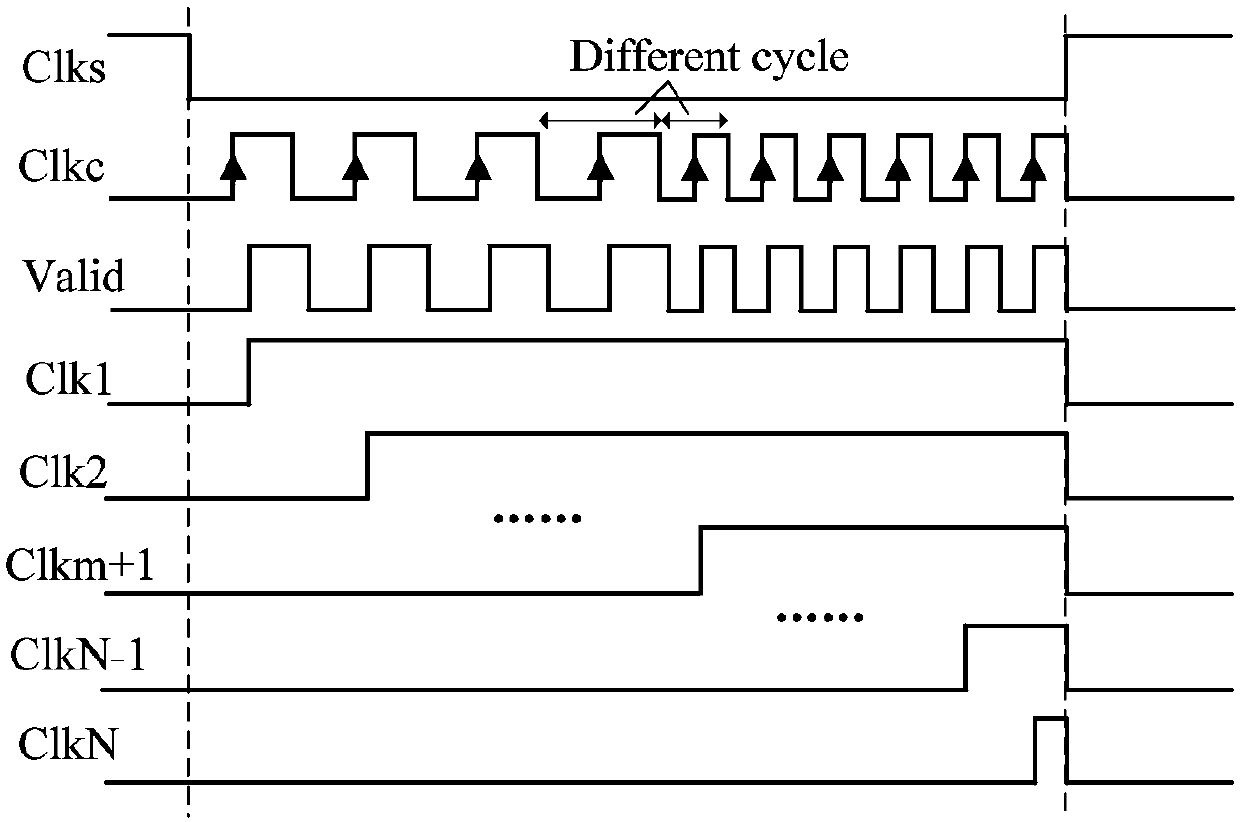

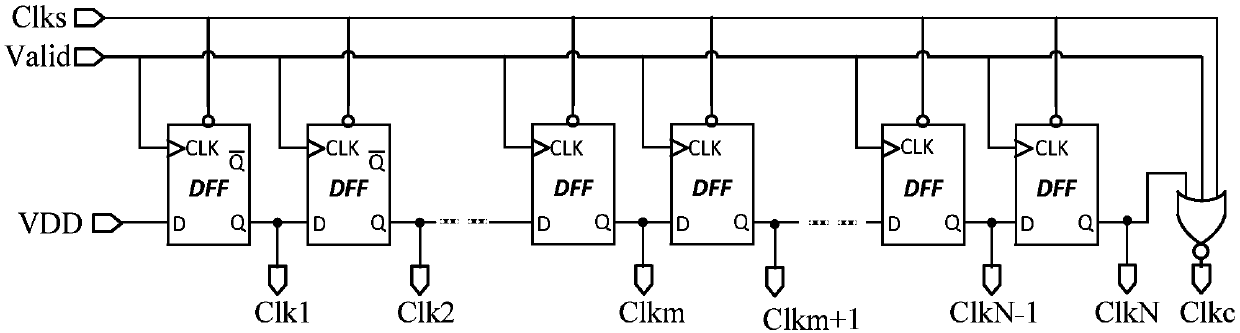

[0019] refer to figure 1 , the present invention's successive approximation analog-to-digital conversion circuit structure includes V INP Differential signal input terminal, V INN Differential signal input terminal, V XP Sample and hold circuit, V XN Sample and hold circuit, two-stage dynamic comparator M1, variable cycle control unit, internal clock generation unit, C P Array switching control unit, C N Array switching control unit, high level signal terminal V REF , low level signal terminal GND and common mode voltage signal terminal V CM . During the sampling phase, the input signal V INP Sampled to the upper plate V of the positive N-bit binary capacitor array through the sampling switch K1 XP , the input signal V INN Sampled to the upper plate V of the negative N-bit binary capacitor array through the sampling switch K2 XN . After the sampli...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com