Constant migration rate method for extracting source/drain parasitic resistance in nanometer MOSFET

A parasitic resistance and mobility technology, applied in electrical digital data processing, CAD circuit design, special data processing applications, etc., to achieve high accuracy, simple operation, and wide application.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0041] In order to enable those skilled in the art to better understand the technical solutions in this application, the technical solutions in this application will be clearly and completely described below in conjunction with embodiments.

[0042] Such as Figure 1-Figure 6 As shown, the present invention discloses a constant mobility method for extracting source / drain parasitic resistance in nano-MOSFET;

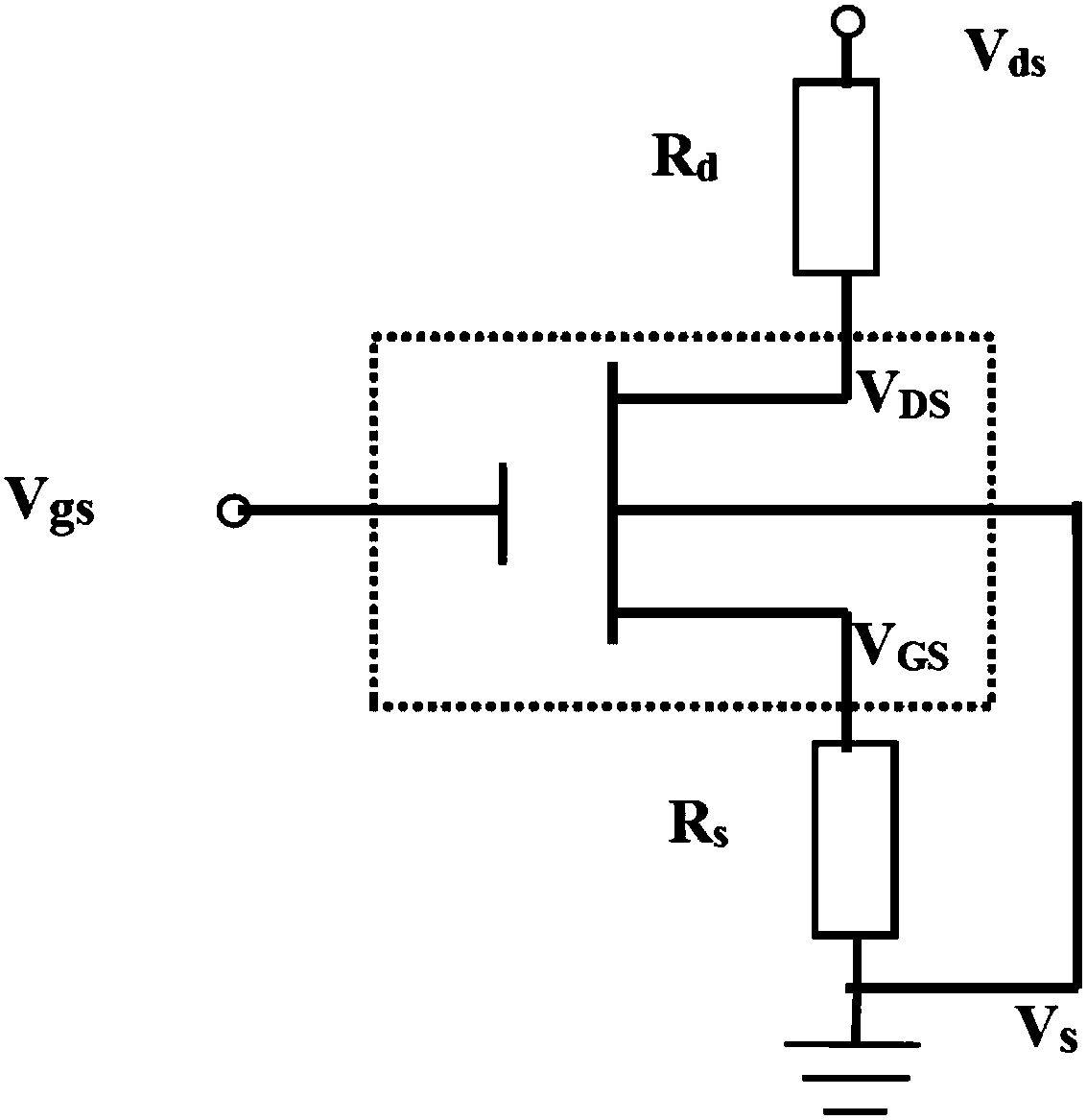

[0043] exist figure 1 Middle: V GS and V DS is the intrinsic voltage of the device circuit, V gs and V ds is the applied bias voltage of the device circuit;

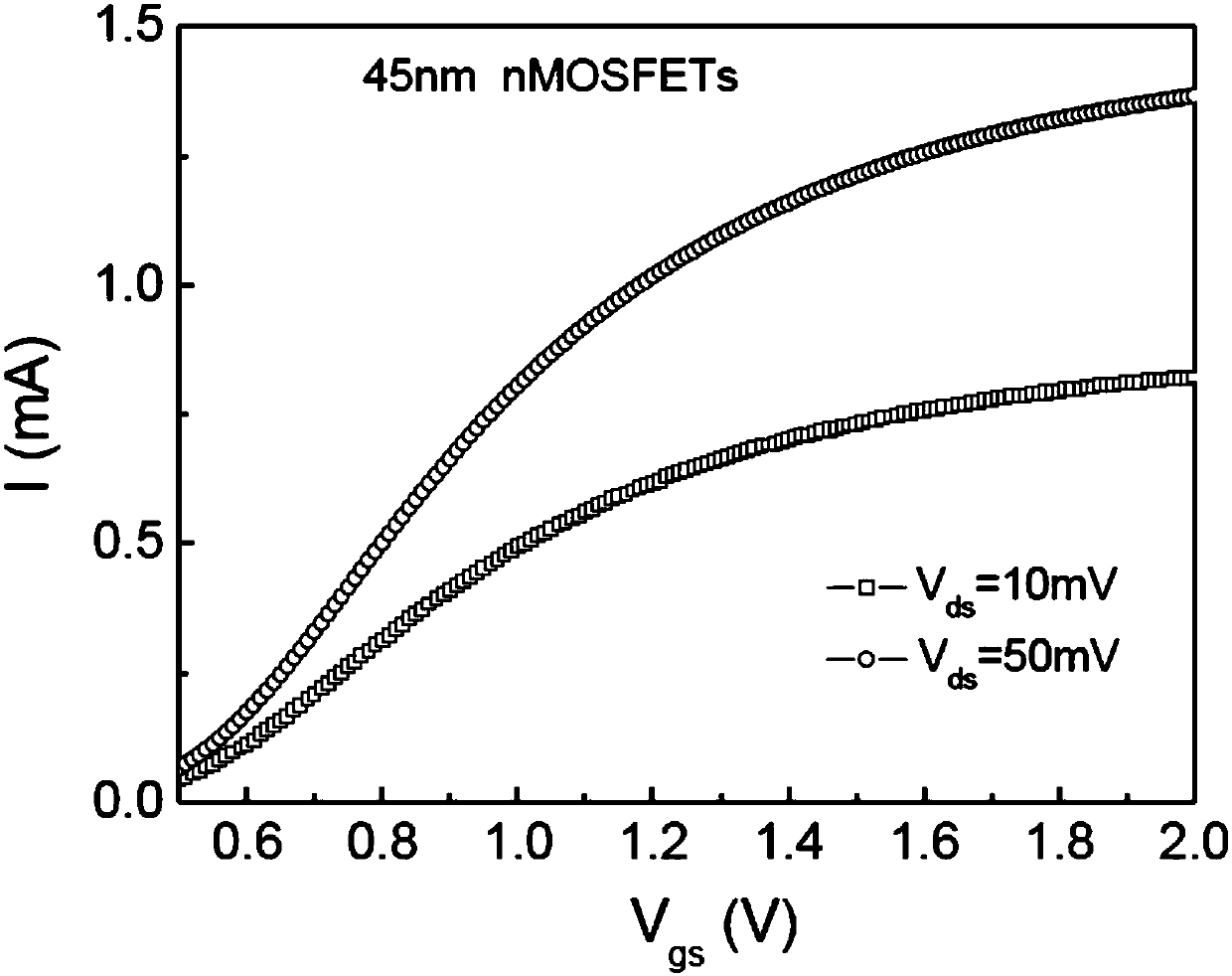

[0044] exist figure 2 Middle: The measurement conditions of the two curves are V ds = 10mV and V ds =50mV;

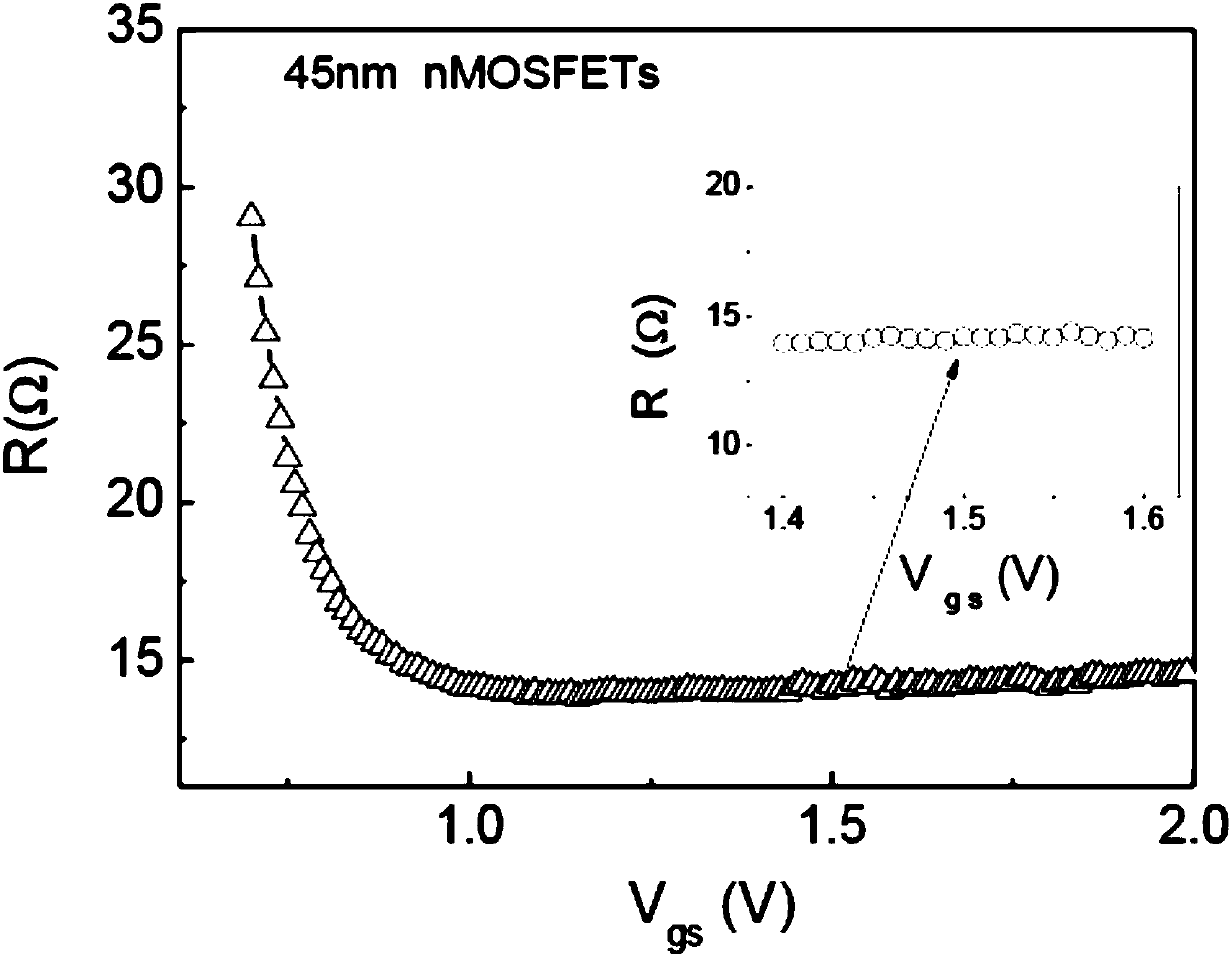

[0045] exist Figure 5 Middle: The points in the figure represent the R values of ten samples, and the solid line is the fitting result of Weibull distribution;

[0046] exist Figure 6 Middle: V in the figure ds When taking a smaller value in the linear region, its change causes a small L ef...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More