I3C bus control interface circuit

An interface circuit and bus control technology, applied in the direction of logic circuit, logic circuit interface device, logic circuit connection/interface layout, etc., to reduce power consumption, ensure speed and performance, and improve equipment performance.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0037] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with the accompanying drawings and embodiments. It should be understood that the specific embodiments described here are only used to explain the present invention, not to limit the present invention.

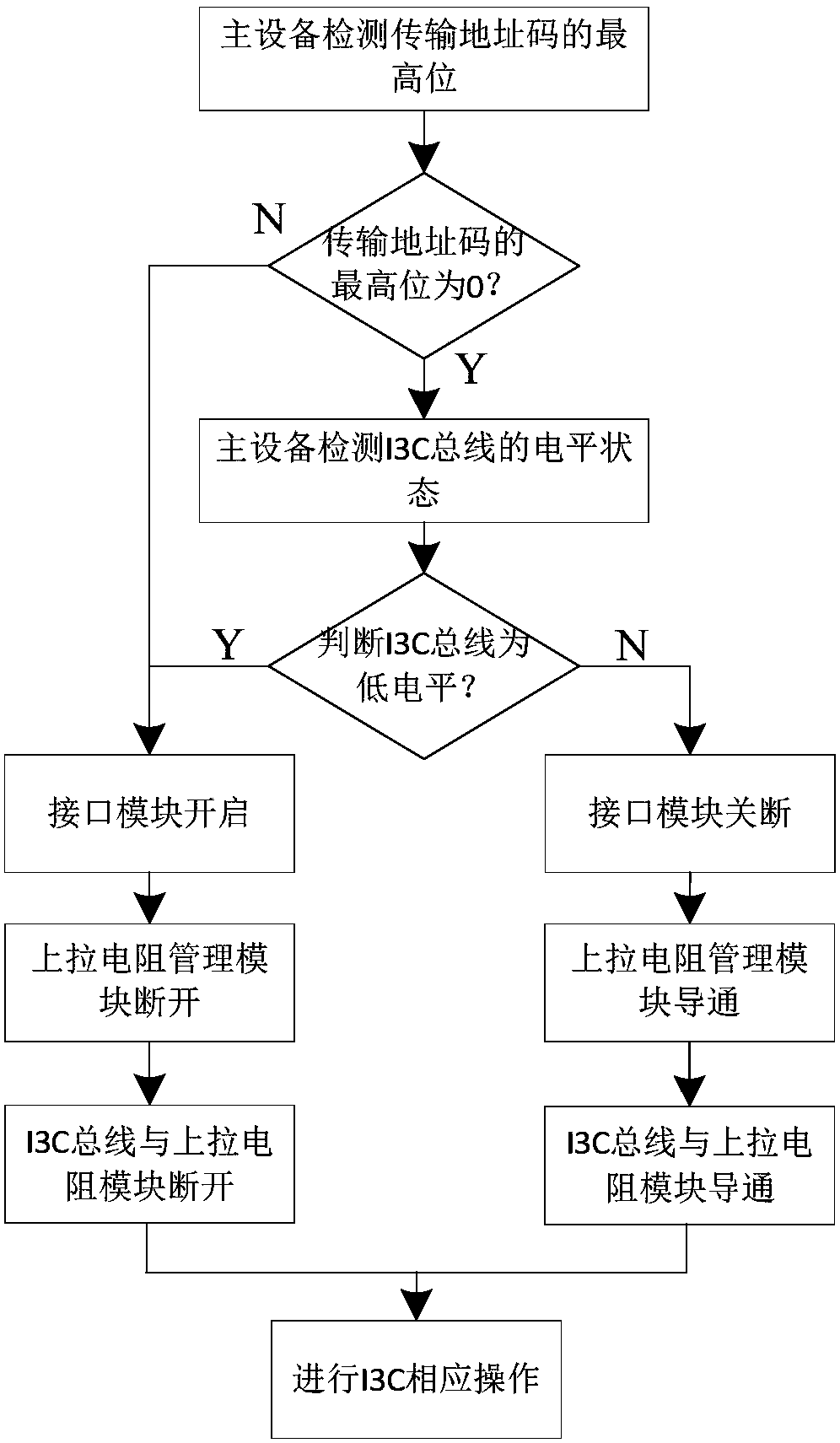

[0038] Please refer to the following Figure 1 to Figure 5 The realization of the present invention is described in detail:

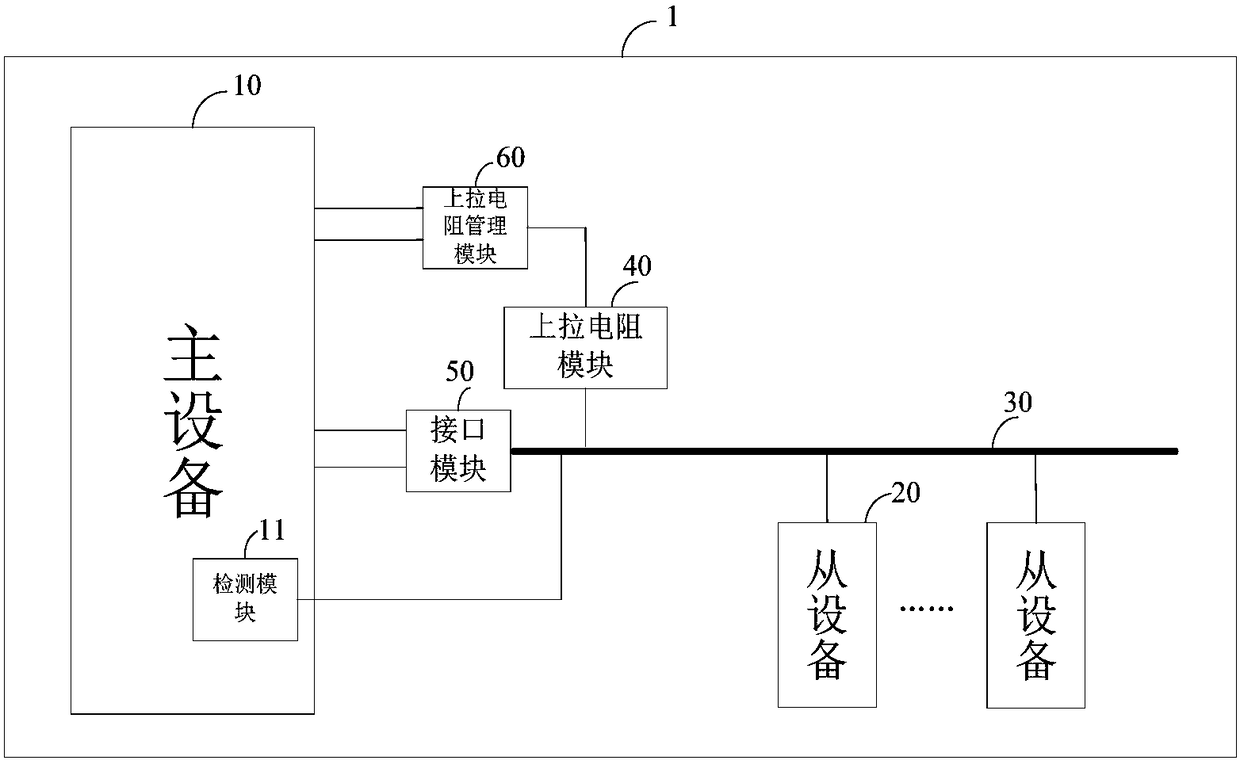

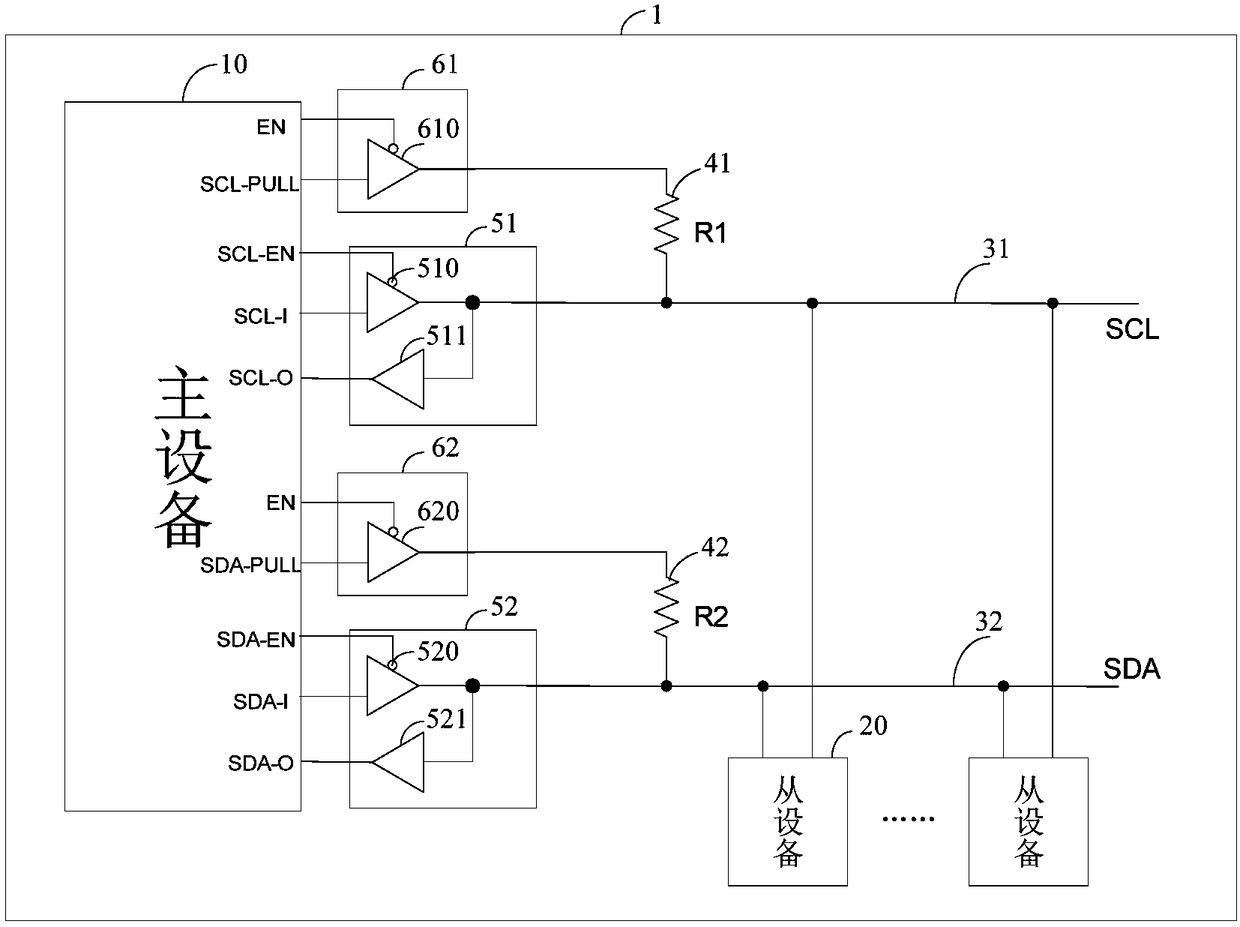

[0039] figure 1 A schematic diagram of the circuit structure of the I3C bus control interface circuit provided by an embodiment of the present invention is shown. For the convenience of description, only the parts related to this embodiment are shown, and the details are as follows:

[0040] Such as figure 1 As shown, a kind of I3C bus control interface circuit provided by the embodiment of the present invention includes a master device 10, at least one slave device 20 and ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More