Planar cascaded semiconductor chip device and cascaded method

A semiconductor and chip-level technology, applied in semiconductor devices, semiconductor/solid-state device manufacturing, semiconductor/solid-state device components, etc., to achieve high surface activity and surface energy, high precision, and prevent pollution

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

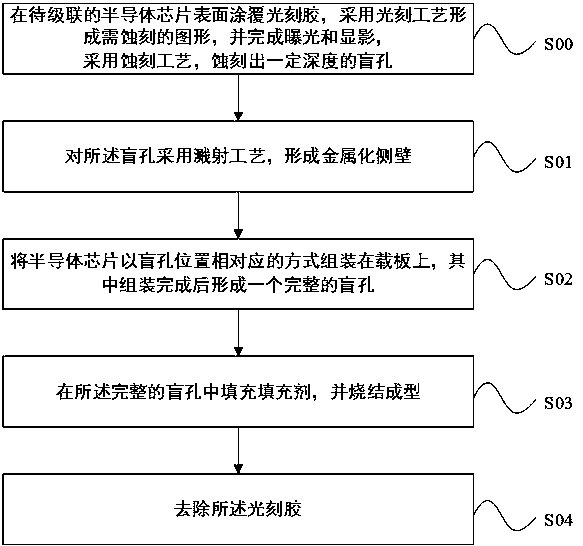

[0040] Further describe the technical scheme of the present invention in detail below in conjunction with accompanying drawing:

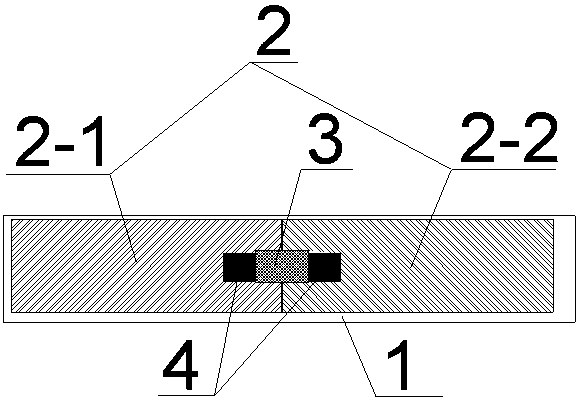

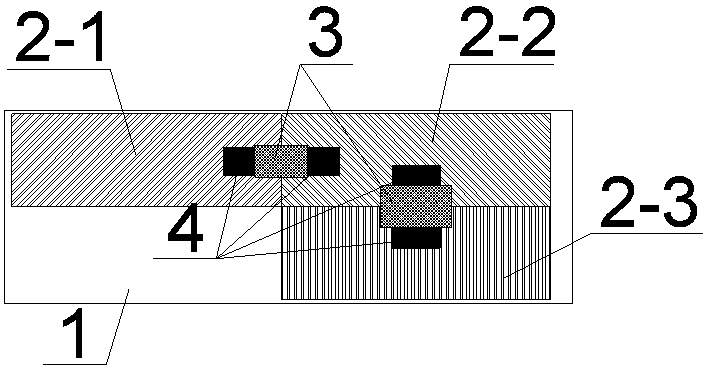

[0041] Such as figure 1 and figure 2 As shown, a planar cascaded semiconductor chip device includes:

[0042] Carrier 1;

[0043] At least two semiconductor chips 2 assembled on the same plane of the carrier plate 1; wherein, each semiconductor chip 2 has at least one blind hole 6, and the positions of the blind holes 6 of the two semiconductor chips 2 correspond to form a complete The blind hole 6; the blind hole 6 includes a metallized side wall;

[0044] The conductive filler 3 filled to the complete blind hole 6 and sintered.

[0045] specifically, figure 1 Shown this device to comprise the embodiment 1 of two semiconductor chips 2, described device comprises:

[0046] Carrier 1;

[0047] The first semiconductor chip 2-1 and the second semiconductor chip 2-2 assembled on the same plane of the carrier plate 1; wherein, in this embodiment,...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More