FPGA-based configurable parallel fast convolution kernel structure

A fast convolution and convolution operation technology, applied in neural architecture, physical implementation, biological neural network model, etc., can solve problems such as insufficient real-time requirements for high-speed signals, low speed and efficiency, and achieve convolution operation. Speed improvements, strong encapsulation and stylized, easy to instantiate effects

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0015] In order to illustrate the embodiments of the present invention more clearly, the present invention will be further described below with reference to the accompanying drawings.

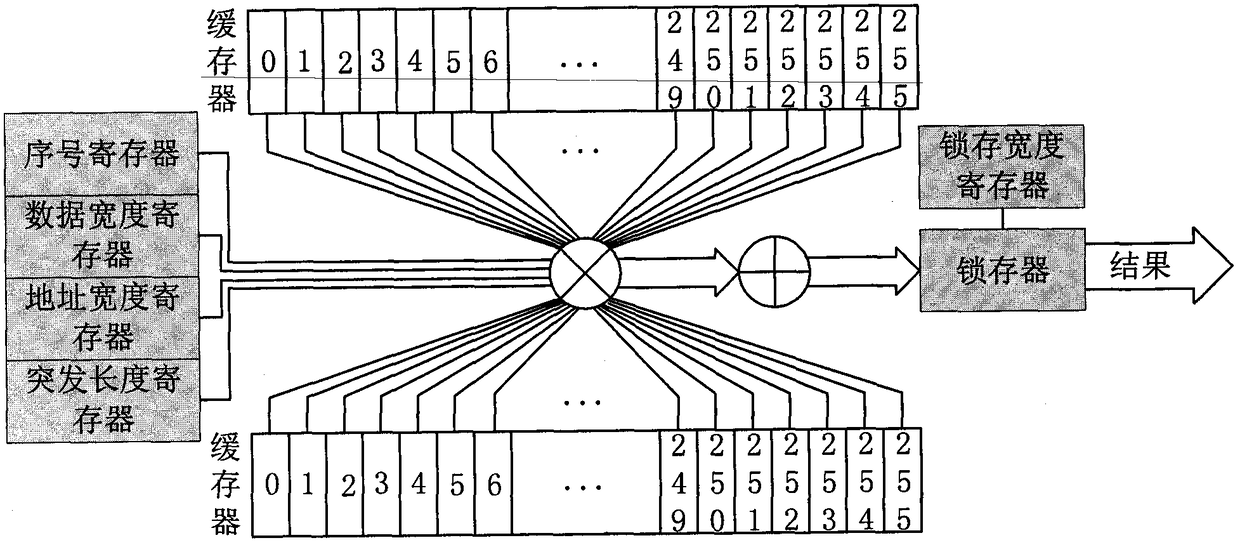

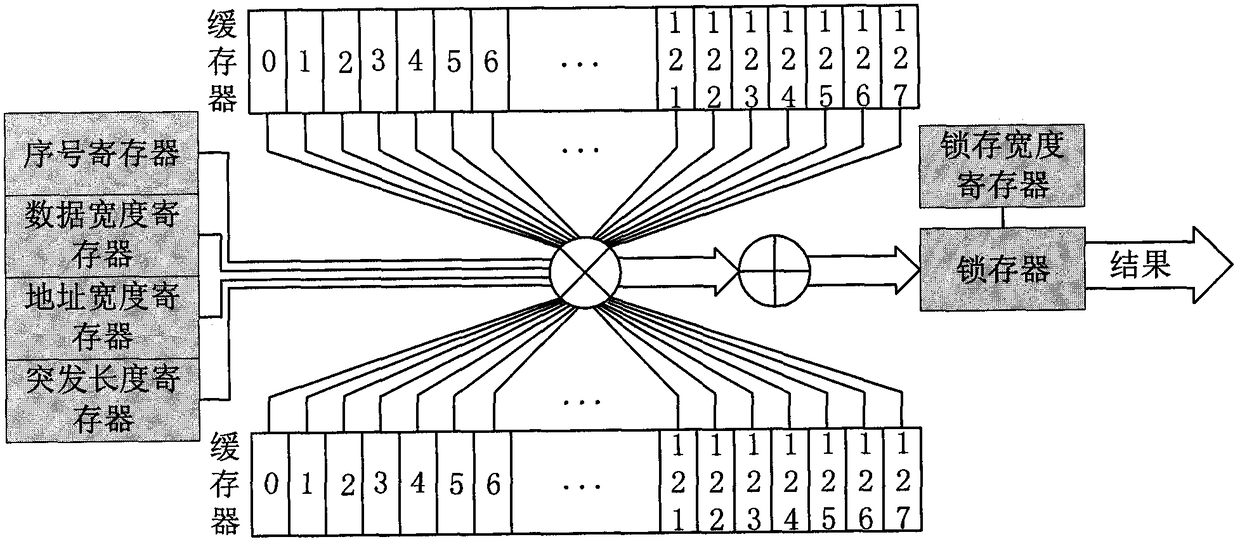

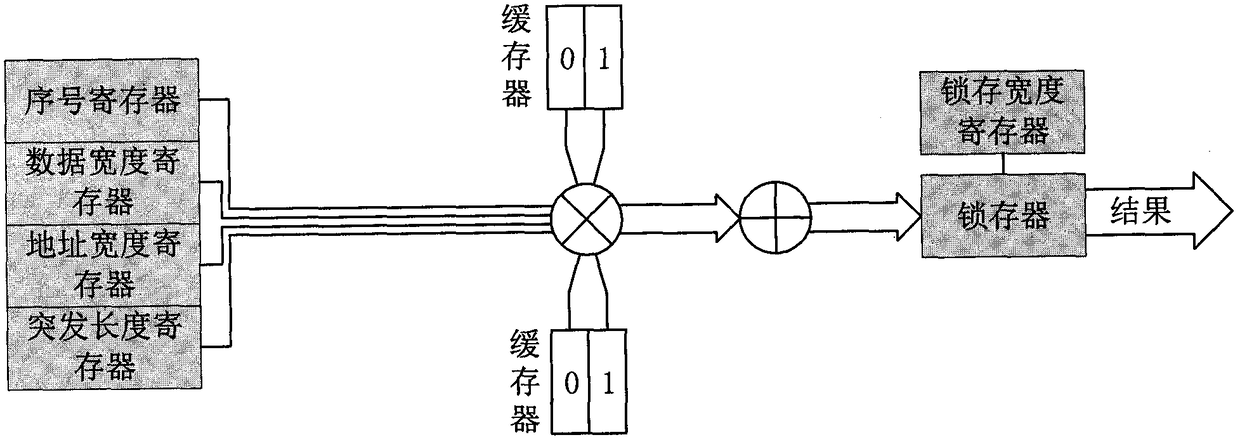

[0016] When the user needs to increase the speed of the convolution operation by 256 times, 256 configurable parallel fast convolution cores should be instantiated. The serial number register assignment of each core starts from 0 to 255, and the burst length register is set to 256. Due to the excessive number, only a few key positions of the hardware structure of the configured parallel fast convolution kernel are listed: figure 1 Shown is the fast convolution kernel with serial number 0, such as figure 2 Shown is the fast convolution kernel with serial number 127, such as image 3 Shown is the fast convolution kernel with serial number 254, such as Figure 4 Shown is the fast convolution kernel with serial number 255. When the width of the two sequences to be convolved is 12bit and the depth is...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More