Asynchronous clock generation circuit suitable for 2-bit-per-cycle SAR ADC

A technology for generating asynchronous clocks and circuits, applied in electrical components, electrical signal transmission systems, signal transmission systems, etc., can solve the problems of increasing system complexity and design difficulty, and achieve avoidance of synchronous metastable states, compact timing, and The effect of speeding up the conversion rate

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0024] The technical solutions and beneficial effects of the present invention will be described in detail below in conjunction with the accompanying drawings.

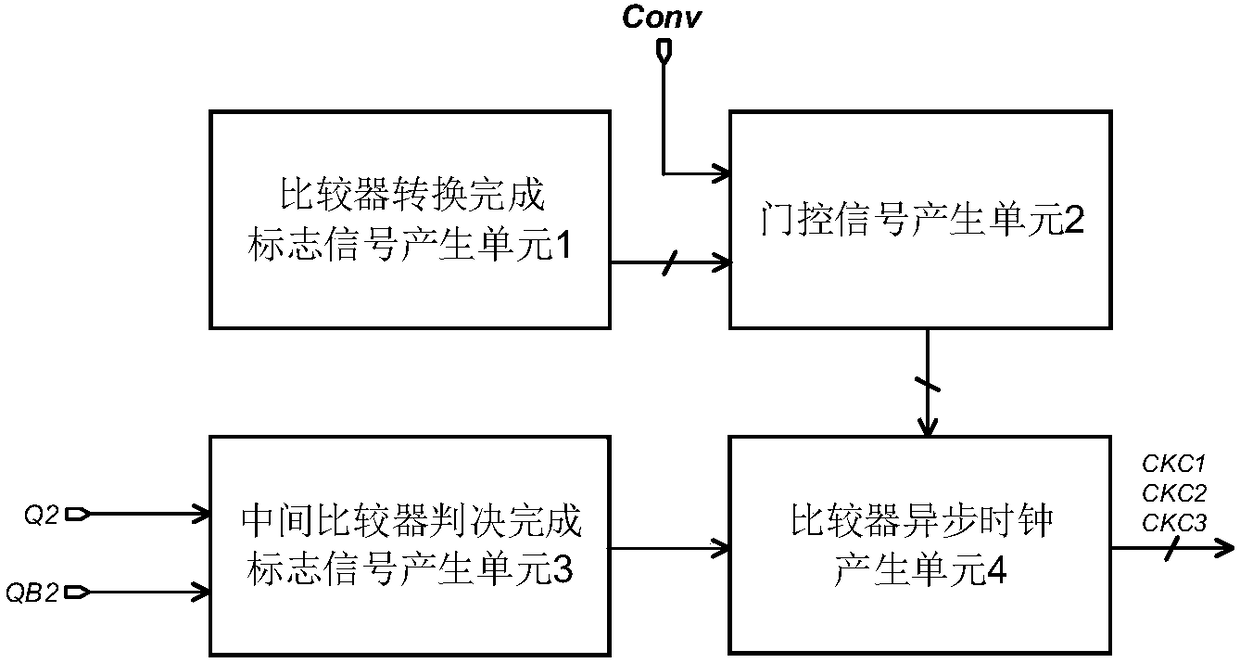

[0025] Such as figure 1 As shown, the present invention provides an asynchronous clock generation circuit suitable for 2-bit-per-cycle SAR ADC, including a comparator conversion completion flag signal generation unit 1, a gating signal generation unit 2, an intermediate comparator judgment completion flag signal Generating unit 3 and comparator asynchronous clock generating unit 4; wherein, the external clock mainly includes ADC conversion clock Conv, which starts conversion at a high level; the comparator conversion completion flag signal generating unit is used to generate 2-bit-per-cycleSAR ADC Each of the three parallel comparators in the conversion phase is latched to complete the flag signal of the last decision result; the gating signal generation unit uses the conversion clock Conv of the ADC and the output si...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More