Out-of-order block-based processors and instruction schedulers

A processor and scheduler technology, applied in instruction analysis, running instruction conversion, concurrent instruction execution, etc., can solve problems such as continuous improvement in area or performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

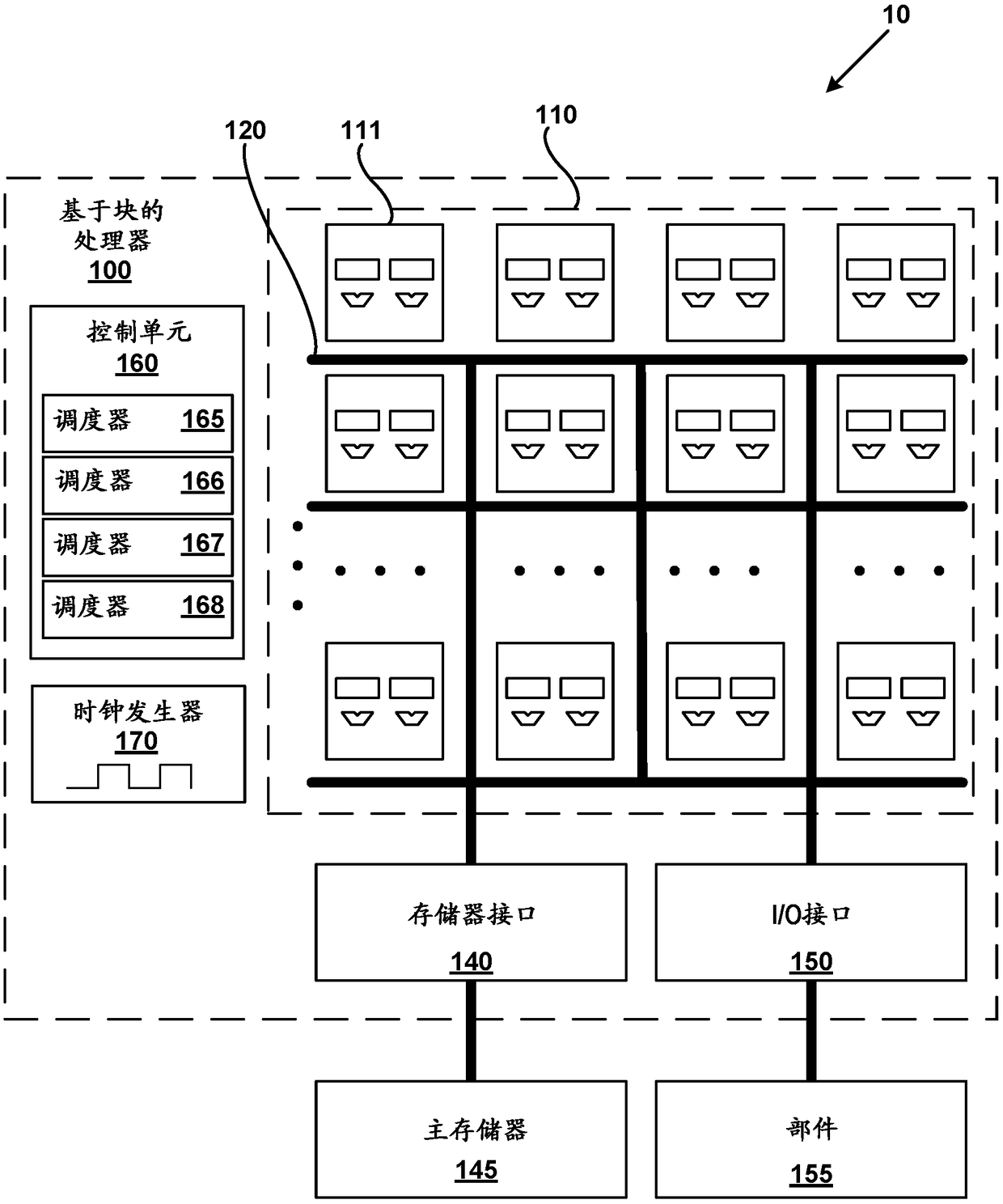

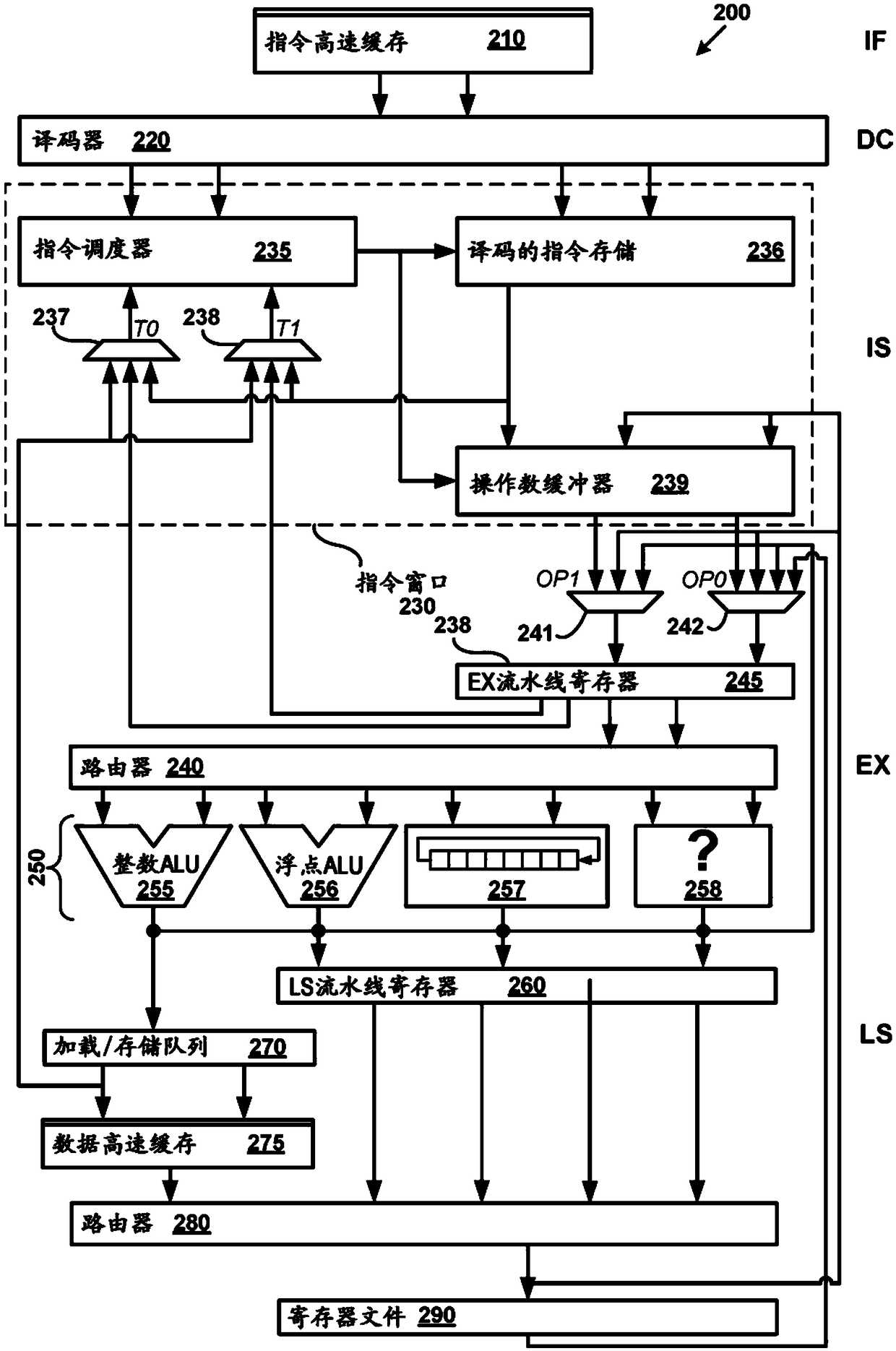

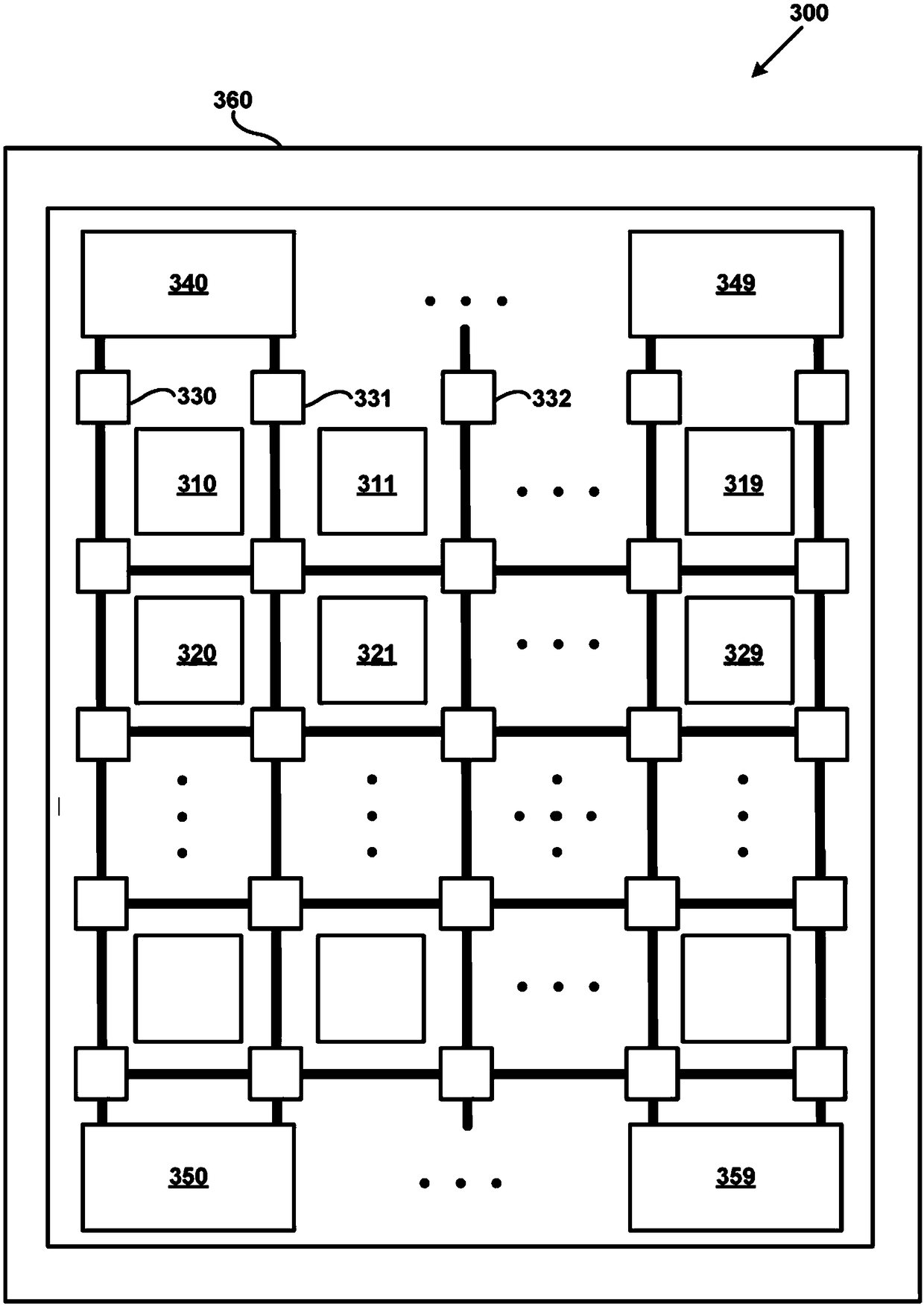

[0019] I. overall consideration

[0020] The present disclosure is set forth in the context of representative embodiments which are not intended to be limiting in any way.

[0021] As used in this application, the singular forms "a", "an" and "the" include plural referents unless the context clearly dictates otherwise. Also, the term "comprising" means "comprising". Furthermore, the term "coupled" encompasses mechanical, electrical, magnetic, optical, and other practical means of coupling or linking items together and does not exclude the presence of intervening elements between coupled items. Additionally, as used herein, the term "and / or" means any one or a combination of multiples of the phrase.

[0022] The systems, methods and devices described herein should not be construed as limiting in any way. Rather, the present disclosure is directed to all novel and non-obvious features and aspects of the various disclosed embodiments both alone and in various combinations an...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More