A method and apparatus for evaluating semiconductor reliability

A reliability and semiconductor technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problems of shortened update cycle and unacceptable reliability test.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

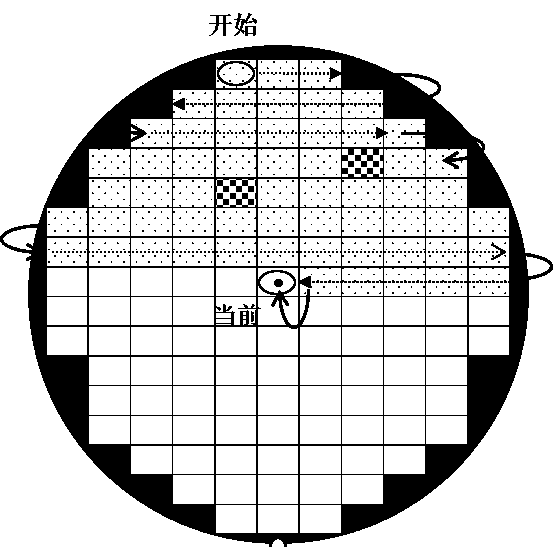

Image

Examples

Embodiment Construction

[0199] The technical solutions of the present invention will be described in further detail below in conjunction with the accompanying drawings and specific embodiments.

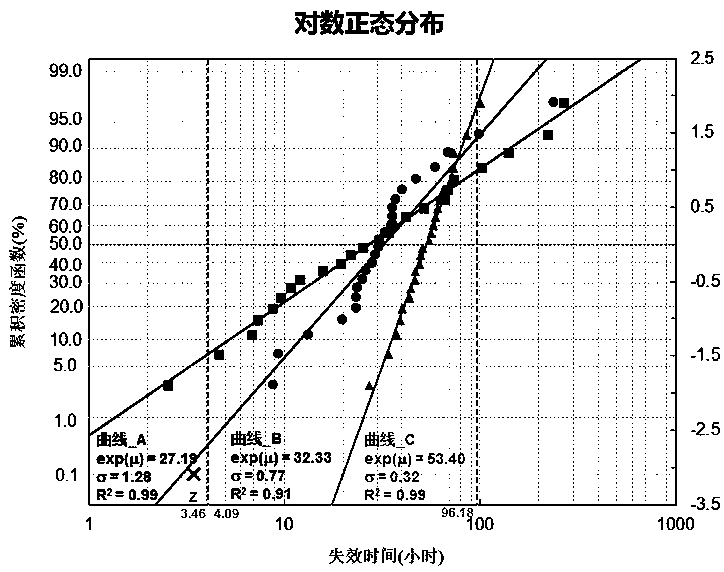

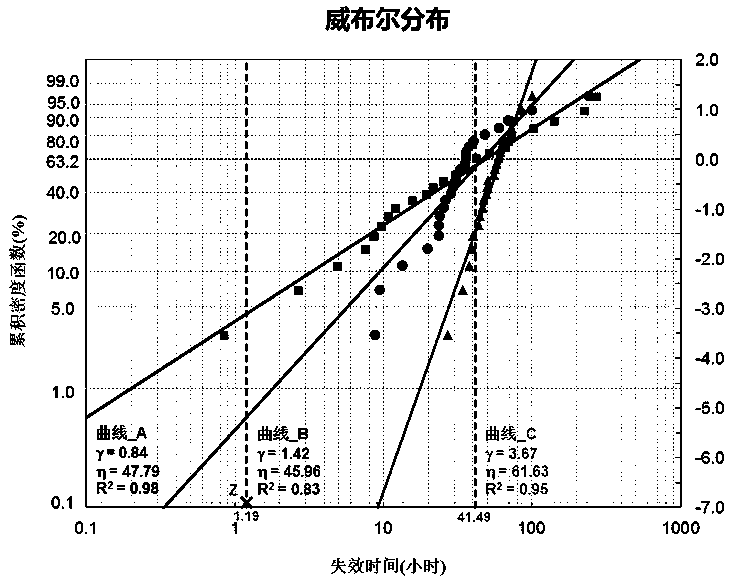

[0200] In practice, when almost identical devices are subjected to the same stress conditions, most of the time they do not fail at the same time due to differences in material microstructure and manufacturing process. Therefore, in the semiconductor reliability evaluation of the present invention, not only Time To Failure (TTF) is of interest, but more precisely, the distribution of Time To Failure is of interest. This reflects the main difference between the present invention and the methods proposed in previous reliability demonstration experiments. Traditionally, two probability density functions have been widely applied to failures in the semiconductor industry: the lognormal and the Weibull distribution. The Weibull distribution is often used to model phenomena that exhibit extreme behavior that encom...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More