Multi-wafer stack structure and forming method thereof

一种堆叠结构、晶圆的技术,应用在电气元件、电固体器件、电路等方向,能够解决硅基板不能适应共用焊盘的需求、厚度限制要求、整体厚度厚等问题,达到减少堆叠厚度、厚度减小、增加封装密度的效果

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

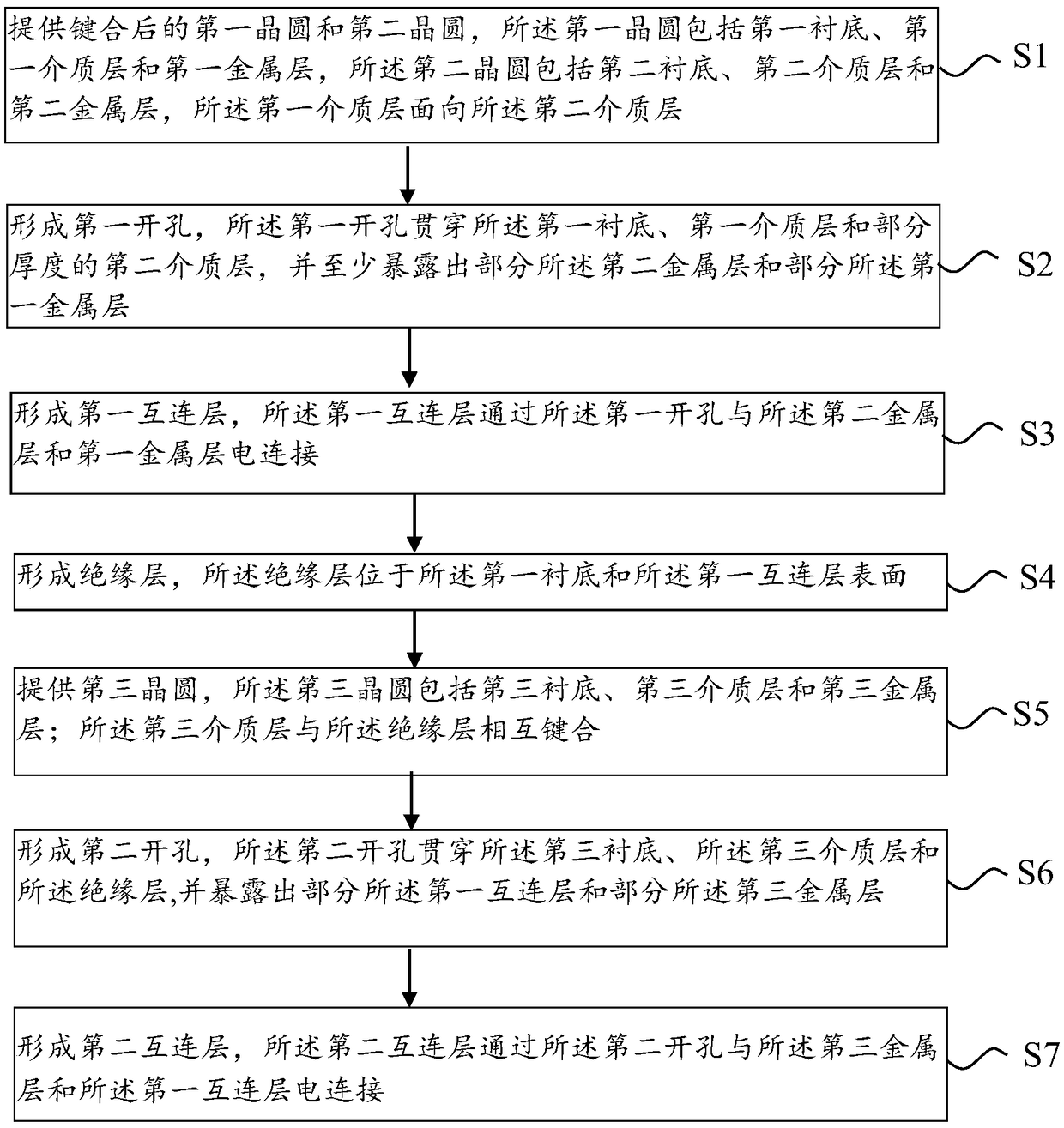

[0049] The manufacturing method of the semiconductor device and the semiconductor device proposed by the present invention will be further described in detail below in conjunction with the accompanying drawings and specific embodiments. The advantages and features of the present invention will become clearer from the following description. It should be noted that all the drawings are in a very simplified form and use imprecise scales, and are only used to facilitate and clearly assist the purpose of illustrating the embodiments of the present invention.

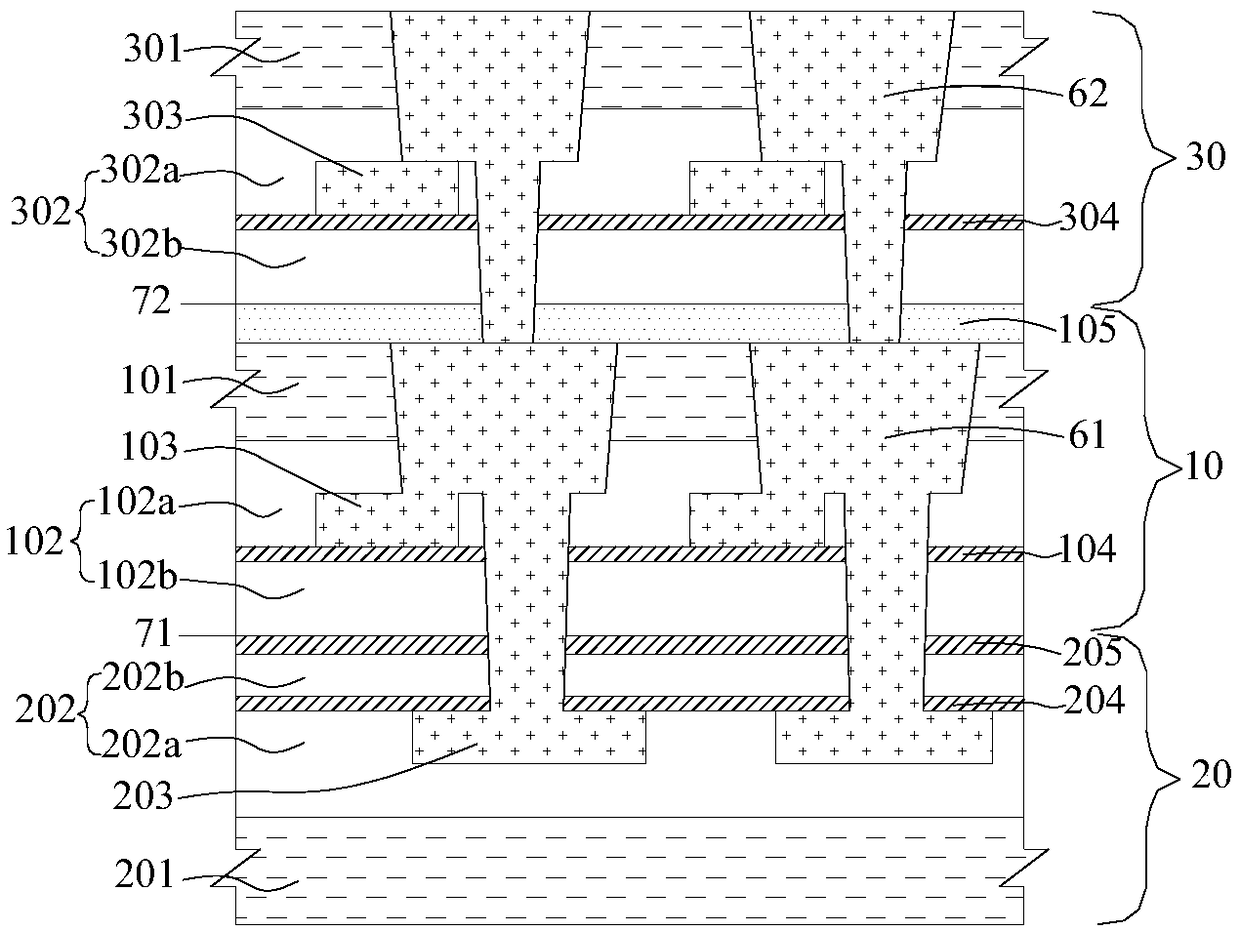

[0050] An embodiment of the present invention provides a multi-wafer stacking structure, such as figure 1 , Figure 10 and Figure 14 shown, including:

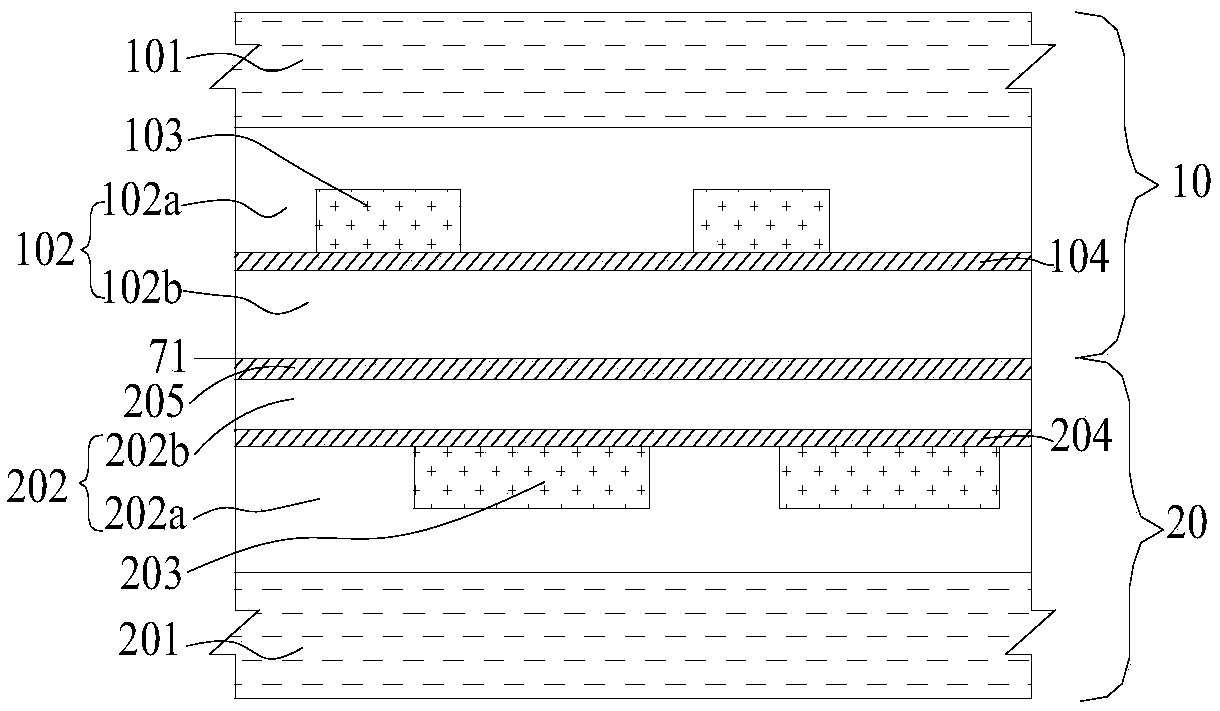

[0051] A first wafer 10, the first wafer 10 comprising a first substrate 101, a first dielectric layer 102 and a first metal layer 103;

[0052] The second wafer 20, the second wafer 20 includes a second substrate 201, a second dielectric layer 202 and a second metal lay...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More