A SoC system-on-chip and a peripheral bus switch method thereof

A system-on-chip and bus switching technology, which is applied to the architecture with a single central processing unit and general-purpose stored program computers, etc., can solve problems such as poor real-time performance, SoC and DSP occupation, and impact on execution efficiency, achieving high reliability and increasing parallelism performance, high access efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0043] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

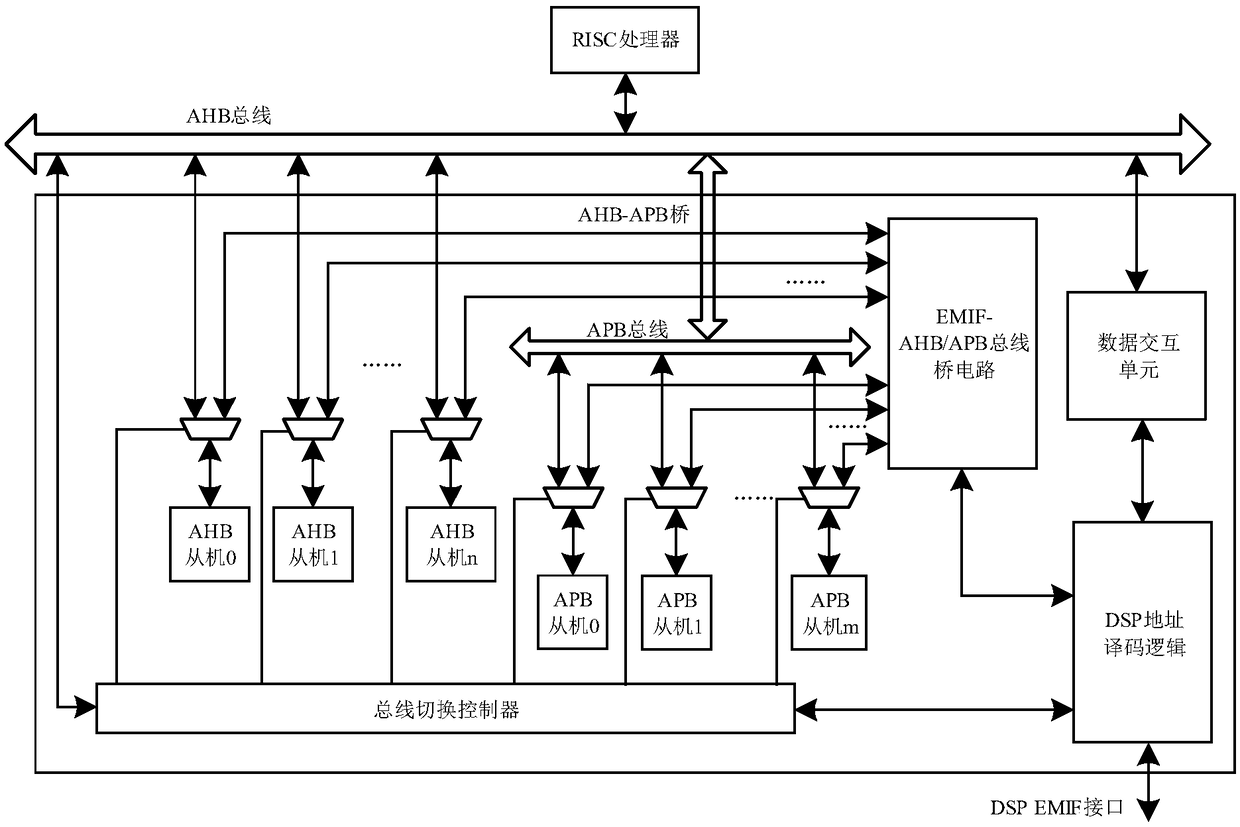

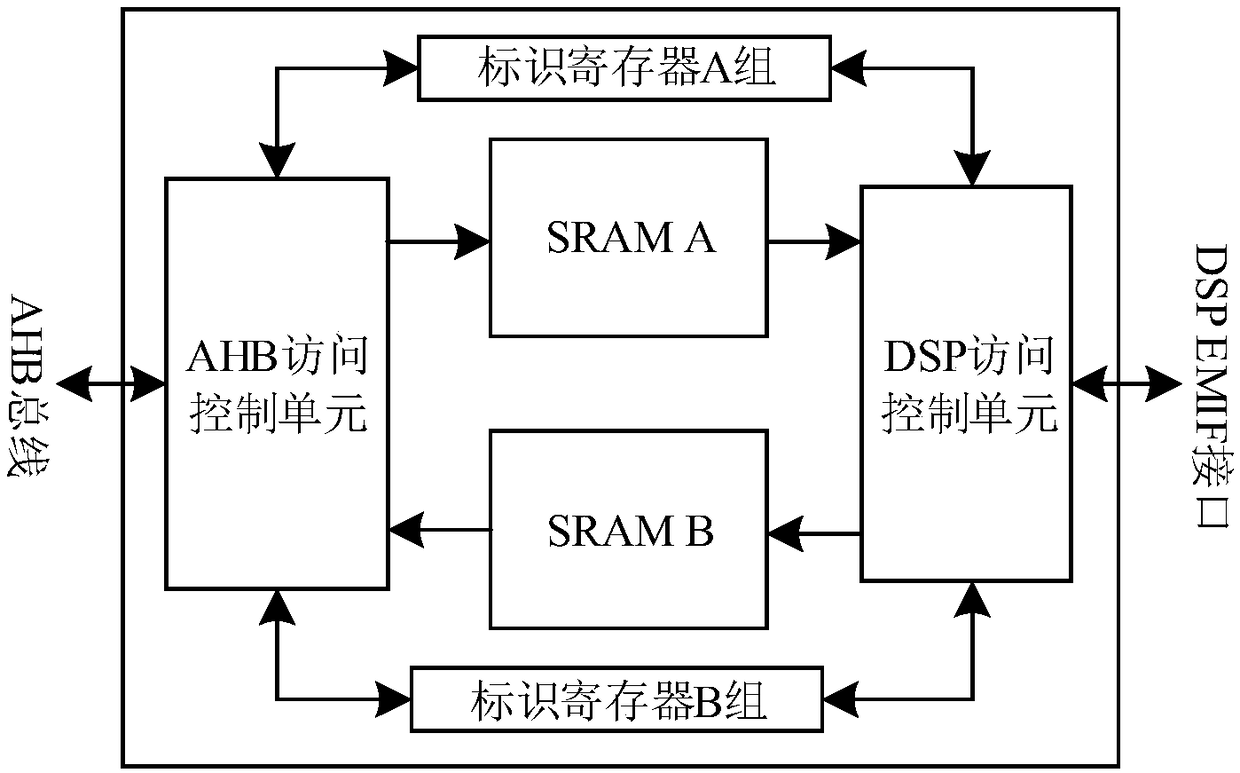

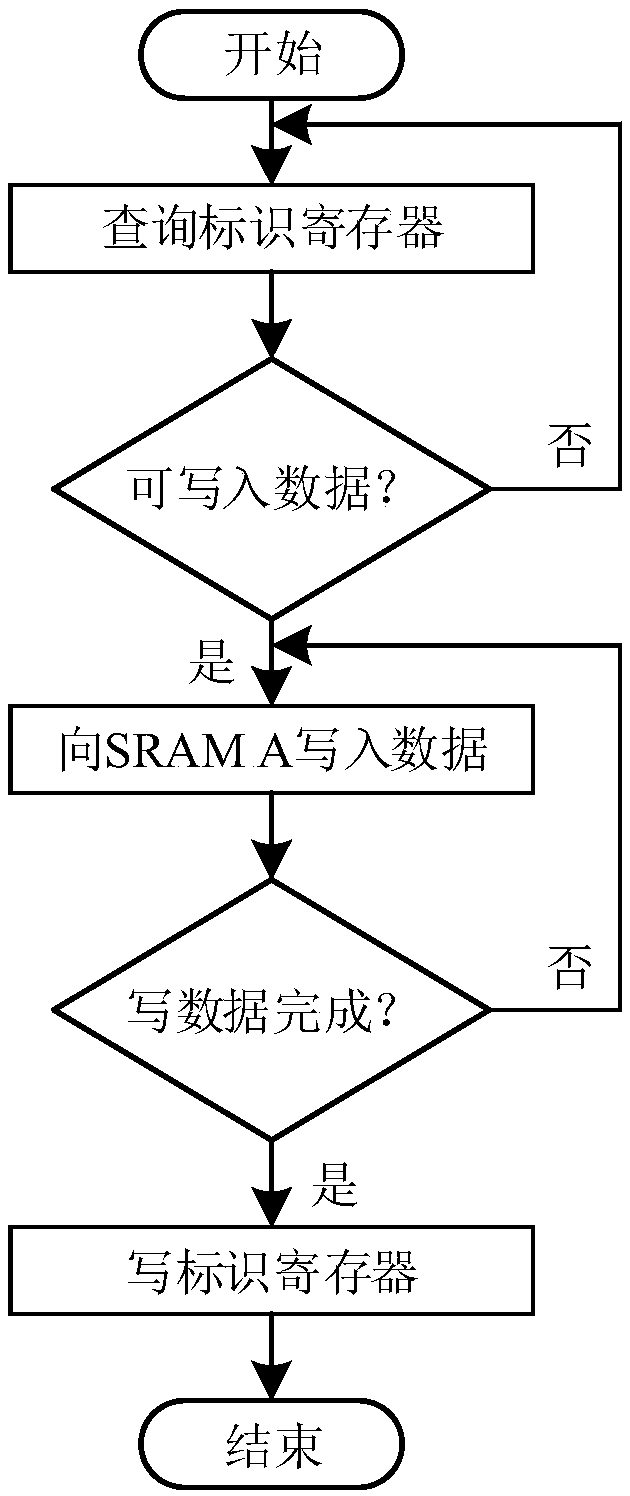

[0044]The present invention is an SoC on-chip system, which is used for the access of off-chip DSP to SoC on-chip peripherals, and simultaneously provides an on-chip bus switching method in which DSP and on-chip RISC processor can access and control on-chip peripherals in time-sharing, which can realize external The direct access of DSP to resources on SoC chip realizes the mechanism of data interaction between DSP and RISC processor on chip through dual-port RAM. To improve the processing efficiency in the DSP+SoC computer system, the SoC system on chip proposed by the present invention enables DSP to access SoC on-chip resources through EMIF and to perform data interaction with the on-chip RISC processor. In order to realize the control of the on-chip peripherals by the DSP, the bridge circ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More