Three-dimensional semiconductor device

A semiconductor, three-dimensional technology, applied in the field of three-dimensional semiconductor devices, can solve problems such as complex process control, and achieve the effect of improving the reliability of electrical connections

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

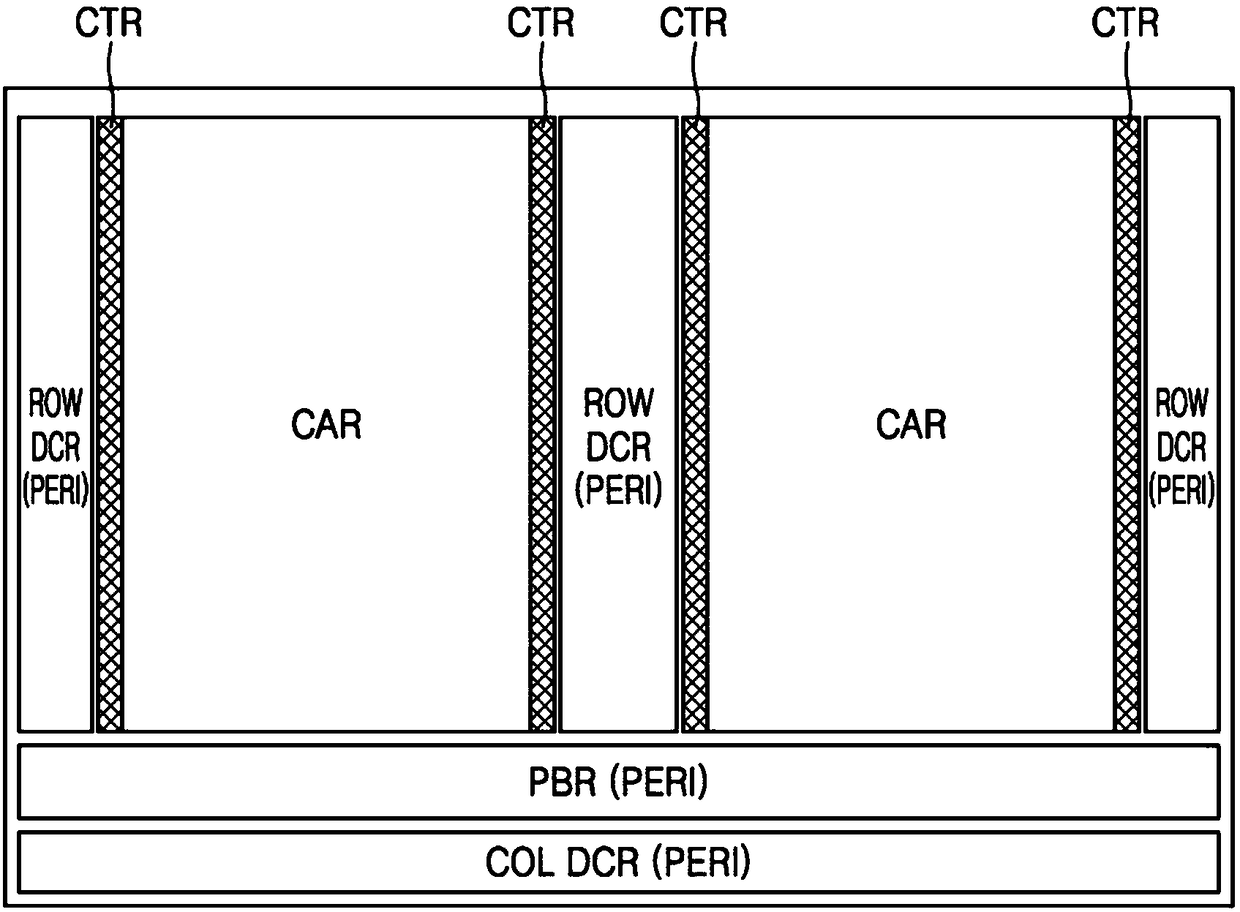

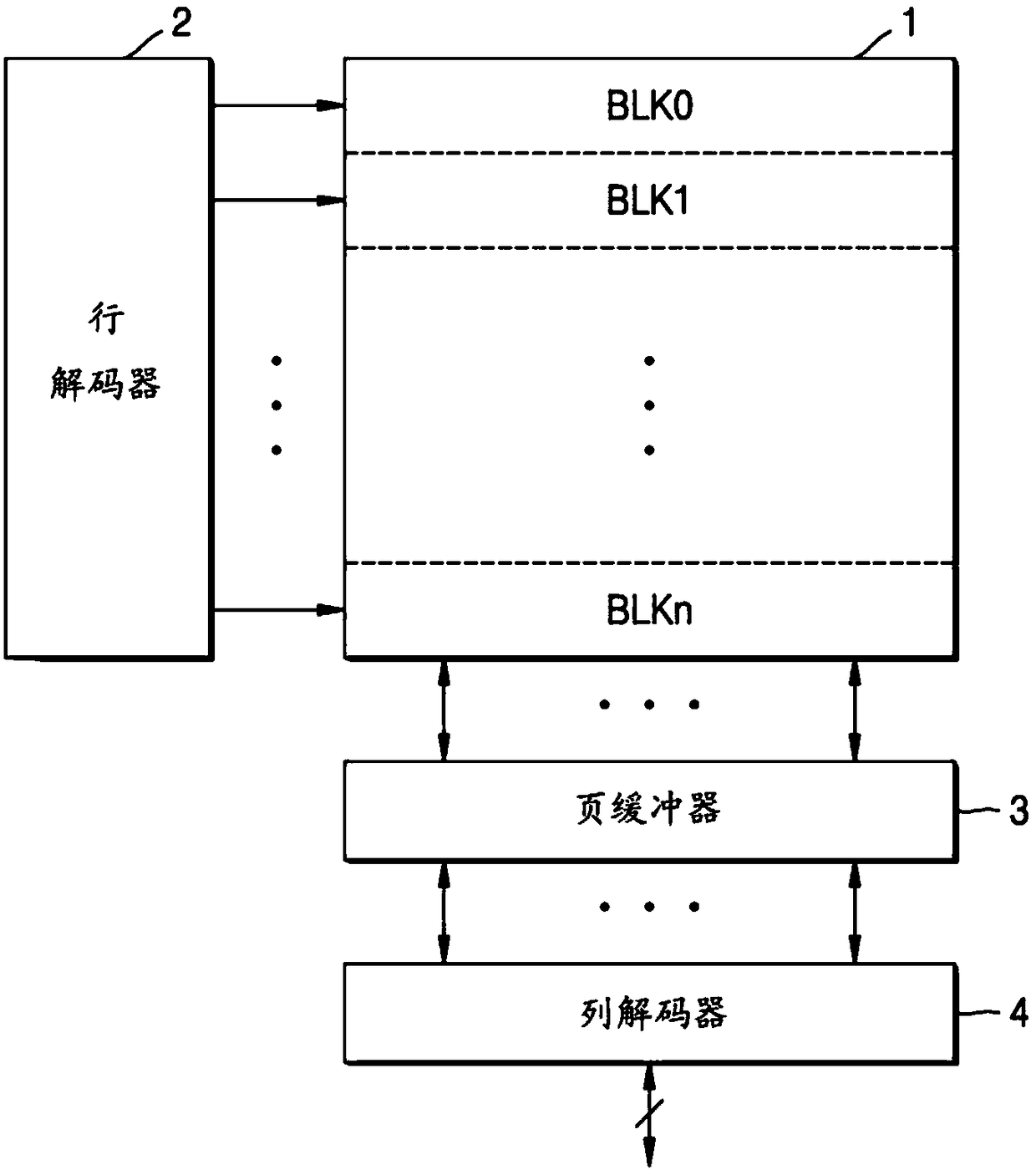

[0024] figure 1 is a plan view illustrating a schematic diagram of a three-dimensional semiconductor device according to an example embodiment, figure 2 is shown based on figure 1 A block diagram of a three-dimensional semiconductor device of the illustrated embodiment.

[0025] refer to together figure 1 and 2 , the three-dimensional semiconductor device may include a cell array region CAR and a peripheral circuit region PERI. The peripheral circuit region PERI may include a row decoder region ROW DCR, a page buffer region PBR, and a column decoder region COL DCR. The contact region CTR may be disposed between the cell array region CAR and the row decoder region ROW DCR.

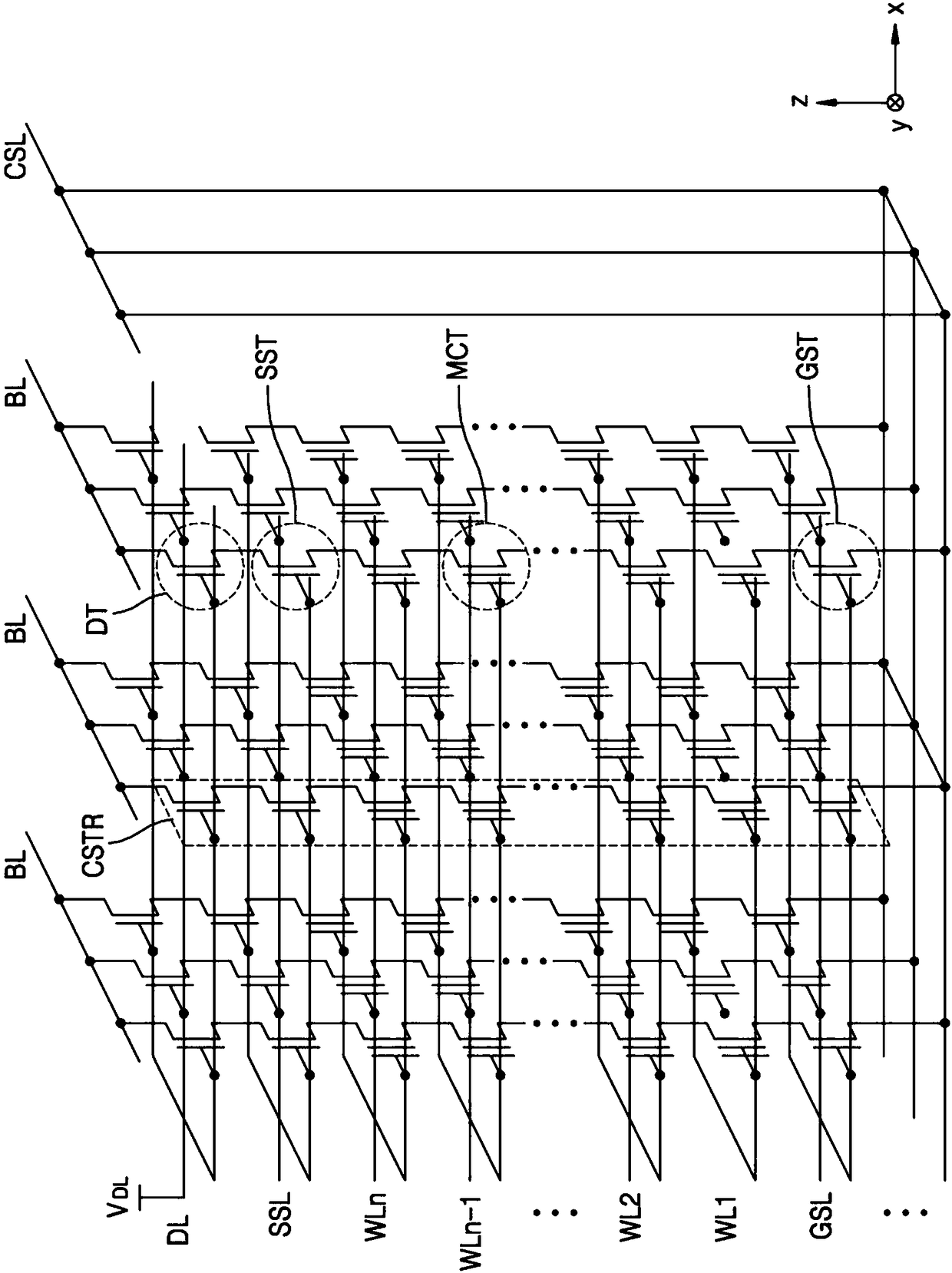

[0026] A three-dimensional memory cell array 1 including a plurality of memory cells may be arranged in the cell array region CAR. The memory cell array 1 may include a plurality of memory cells, and a plurality of word lines and a plurality of bit lines electrically connected to the memory cells. I...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More