Ultrathin semiconductor chip packaging structure and manufacturing process thereof

A technology of chip packaging structure and manufacturing process, which is applied in semiconductor/solid-state device manufacturing, semiconductor devices, semiconductor/solid-state device components, etc., can solve the problem of reducing the width of chip cutting lines, limiting the number of packaged chip pads, and increasing packaging Solve the overall thickness and volume of the structure to achieve the effect of reducing the packaging volume and improving the reliability of electrical connection

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

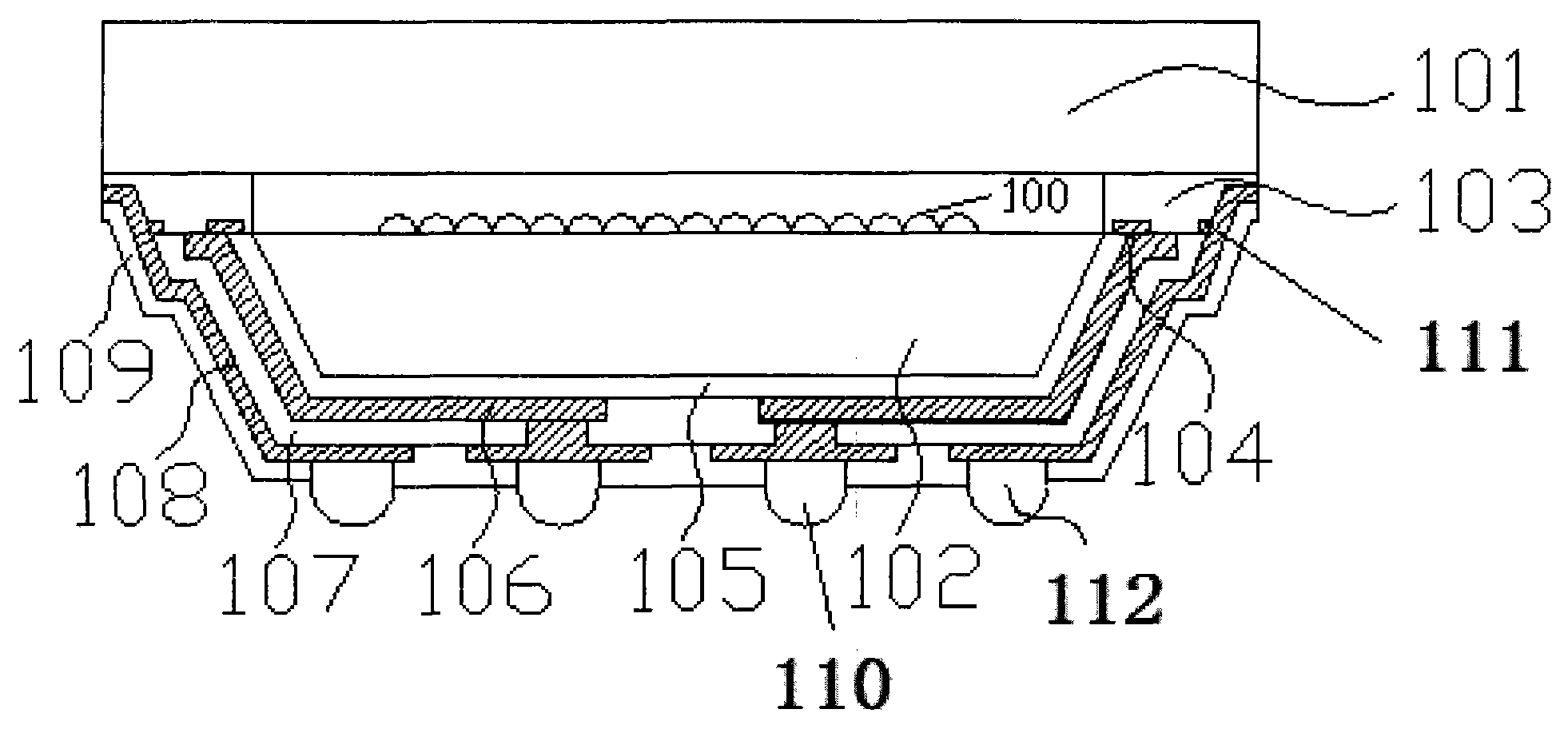

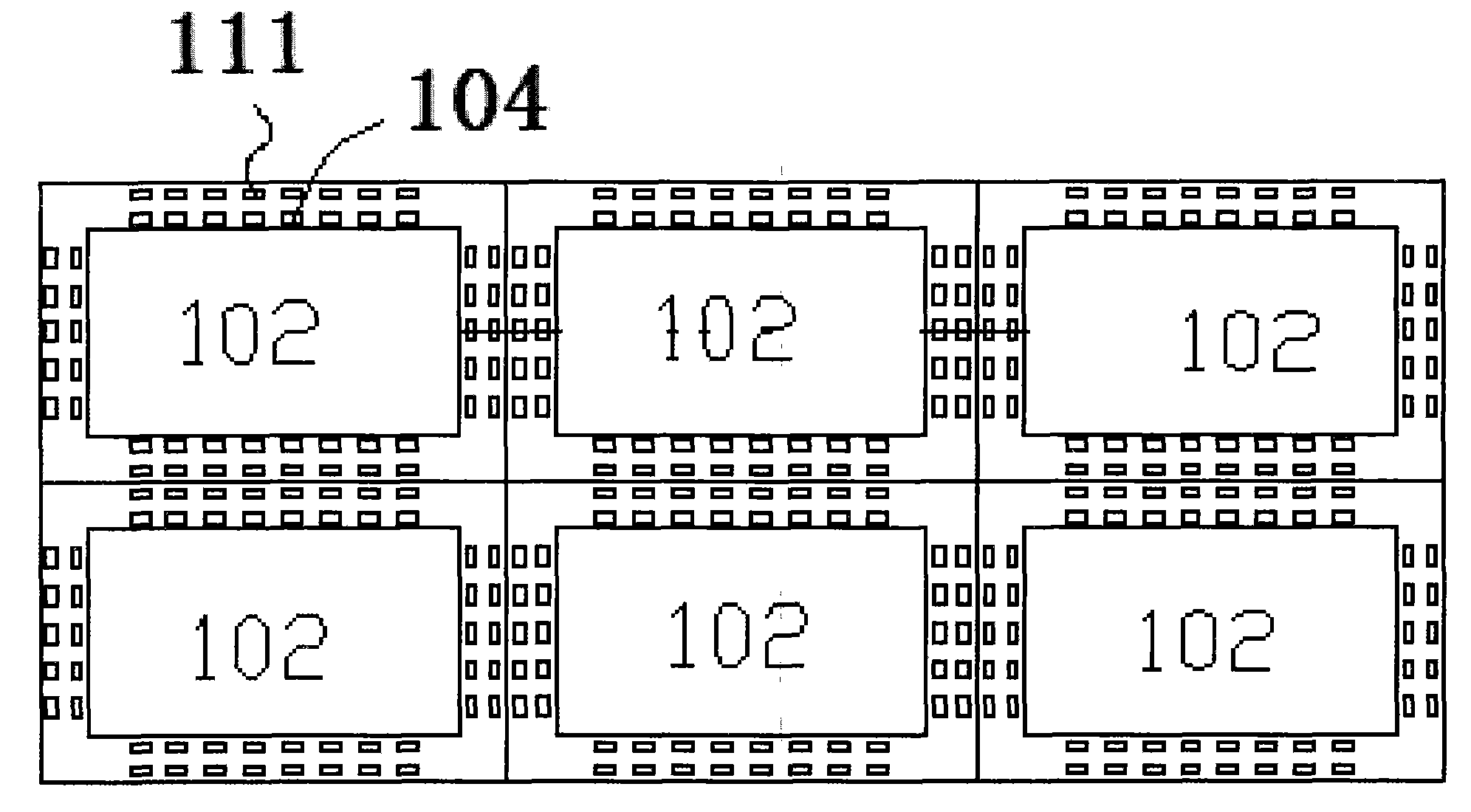

[0035] Example: such as figure 1 As shown, in the ultra-thin semiconductor chip packaging structure provided in this embodiment, the front side of the chip 102 is provided with soldering pads and photosensitive devices 100, and the soldering pads are arranged in double rows around the chip 102, and the inner ones are The first row of welding pads 104, and the second row of welding pads 111 located on the outside, and the two rows of welding pads are electrically connected with the chip 102 through the circuit (not shown in the figure); and the glass substrate 101 described in the present embodiment A cavity wall 103 in a closed-loop structure is provided on it, and the front surface of the chip 102 is pressed against the cavity wall 103 on the glass substrate 101 to form a cavity surrounding the photosensitive device 100 . A first insulating layer 105 is directly deposited on the back of the chip 102, a first wiring layer 106 is deposited on the back of the first insulating la...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More