A fast algorithm for calculating the undercurrent path of an adder based on a memristor array

A fast computing and memristor technology, applied in computing, instruments, electrical digital data processing, etc., can solve the problem of consuming memristor array hardware resources and achieve the effect of improving computing performance

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

[0047] The logical expression of the 1-bit full adder can be expressed as the following two formulas:

[0048]

[0049] C o =AB+AC i +BC i

[0050] For a multi-bit adder, if the calculation is performed step by step in a logical iterative manner, the operation efficiency will be low, thus losing the advantage of memory computing technology due to the reduction of data movement overhead. However, if the carry of all bits can be obtained in an efficient manner, the sum of all bits can be obtained at one time by using the parallel feature of the array structure.

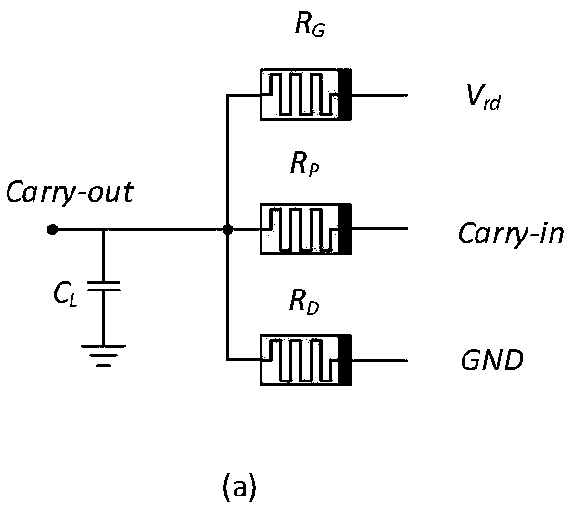

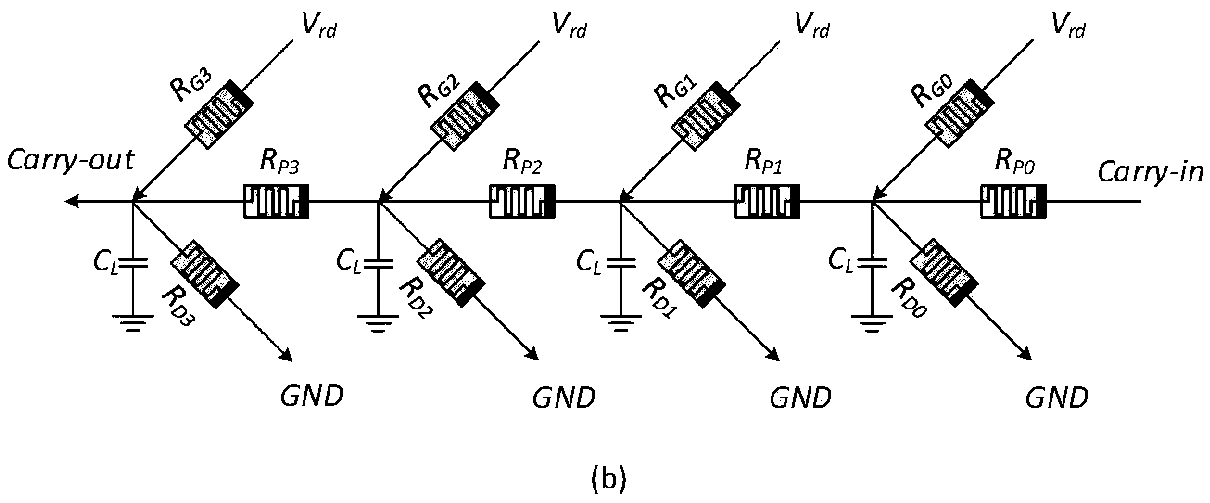

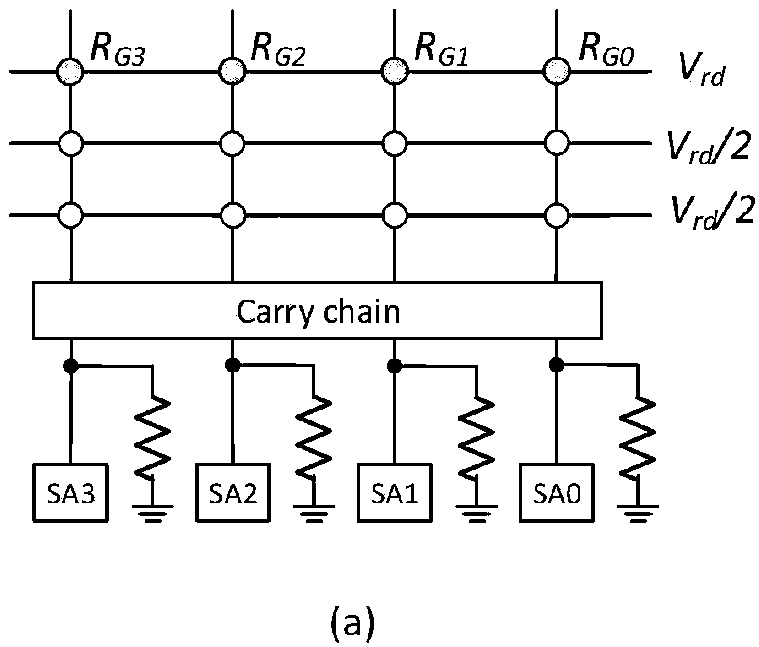

[0051] According to the above thought, Figure 1a and 1b The schematic diagram of the carry calculation based on the memristor is given. Note that the memristor represents the logic value through the resistance value, the low resistance state (LRS) represents logic 1, and the high resistance state (HRS) represents logic 0. in Figure 1a Three undercurrent paths for carry generation are shown:

[0052] 1) Carry ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More