Wiring method for reinforcing protection on important region of metal protection layer at top layer of chip

A top-layer metal and important area technology, applied in the field of chip technology, can solve problems such as simple connection relationship, failure of the protective layer, single step-down form, etc., and achieve the effect of increasing the safety factor, increasing the difficulty, and improving the protection level

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

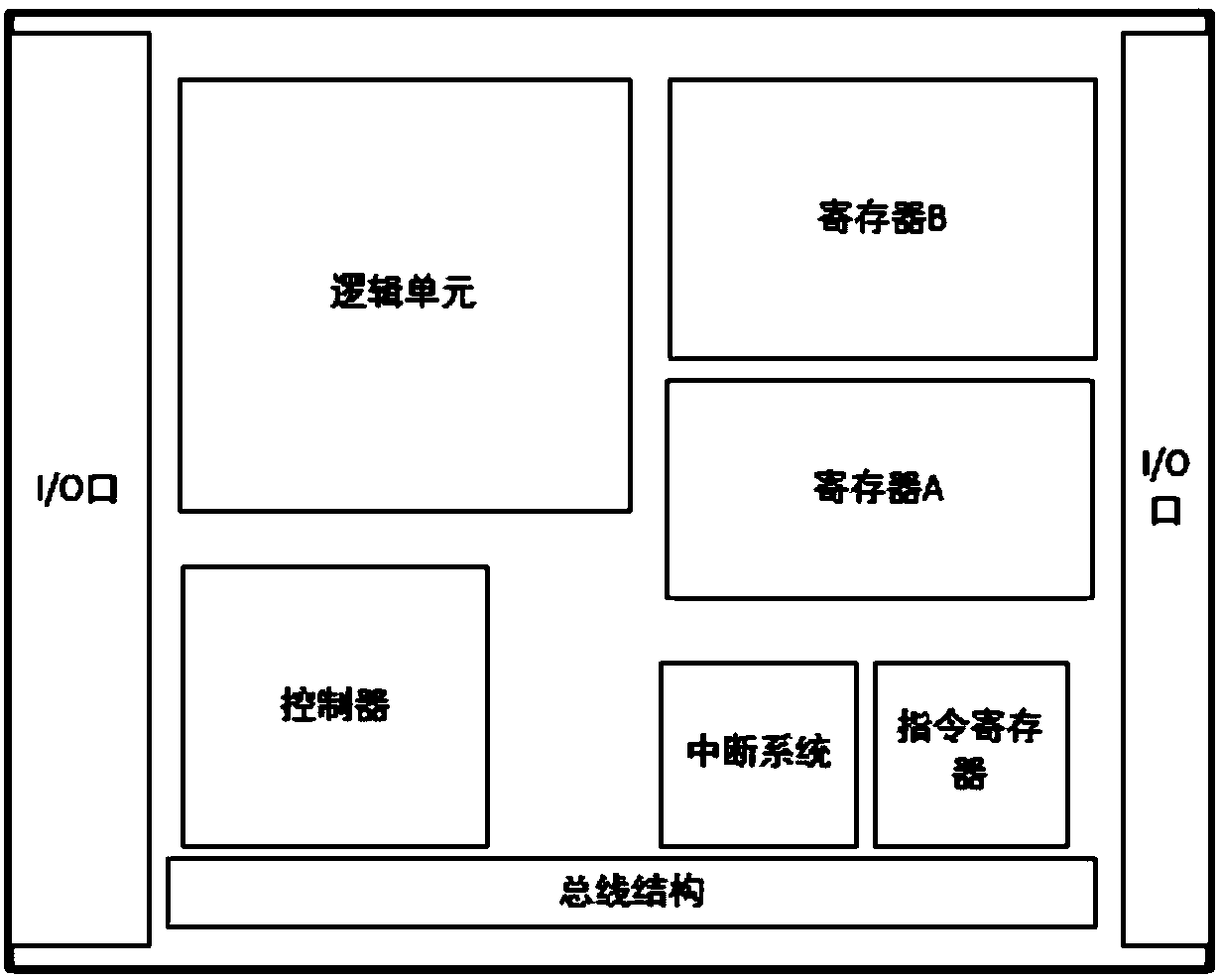

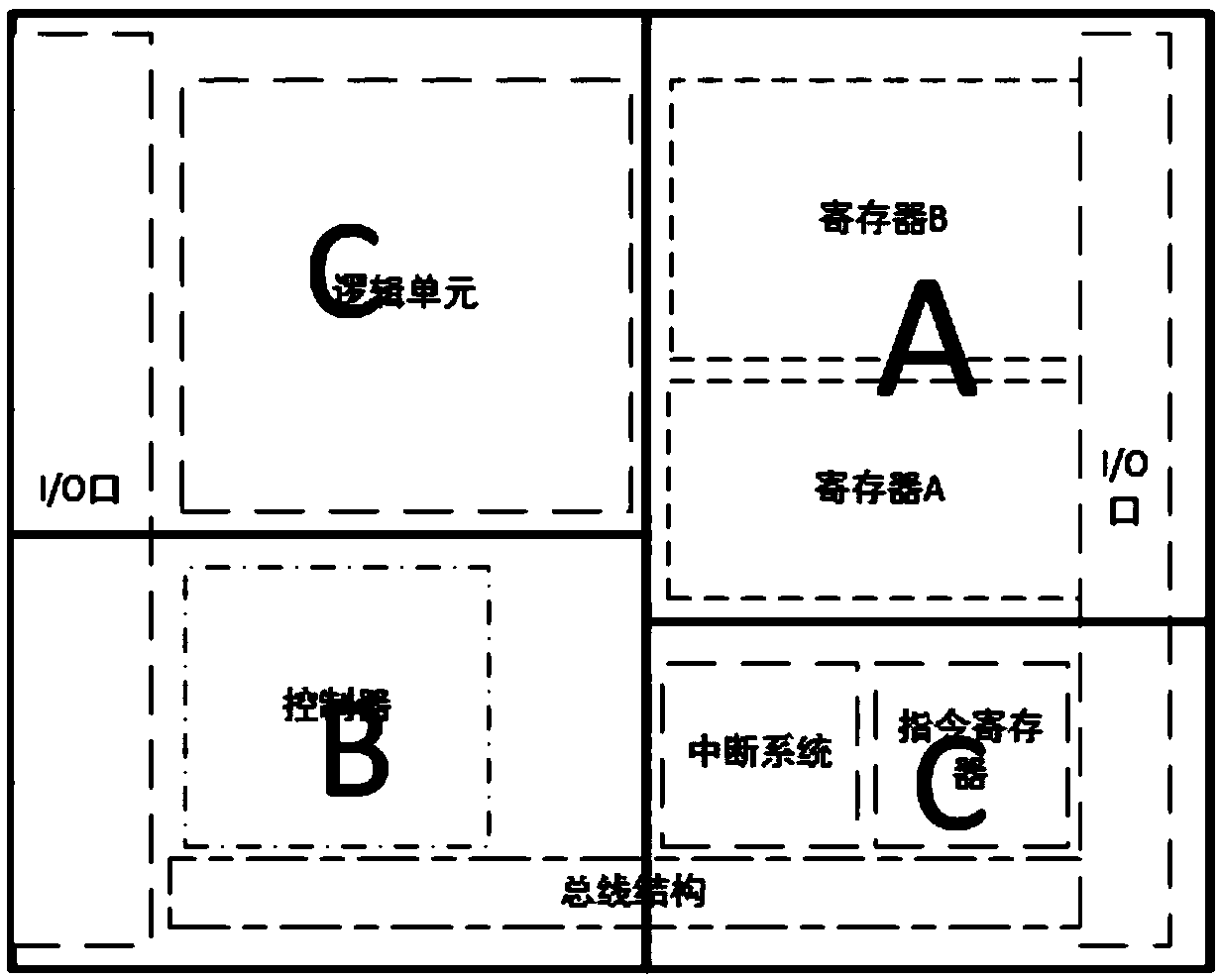

[0020] The present invention has carried out focused evolution and modification for the traditional configuration method of the top metal layer wiring, and can focus on the protection of modules that are easy to leak data on the chip, such as memory modules and data buses.

[0021] 1. The wiring configuration method of the top protective layer:

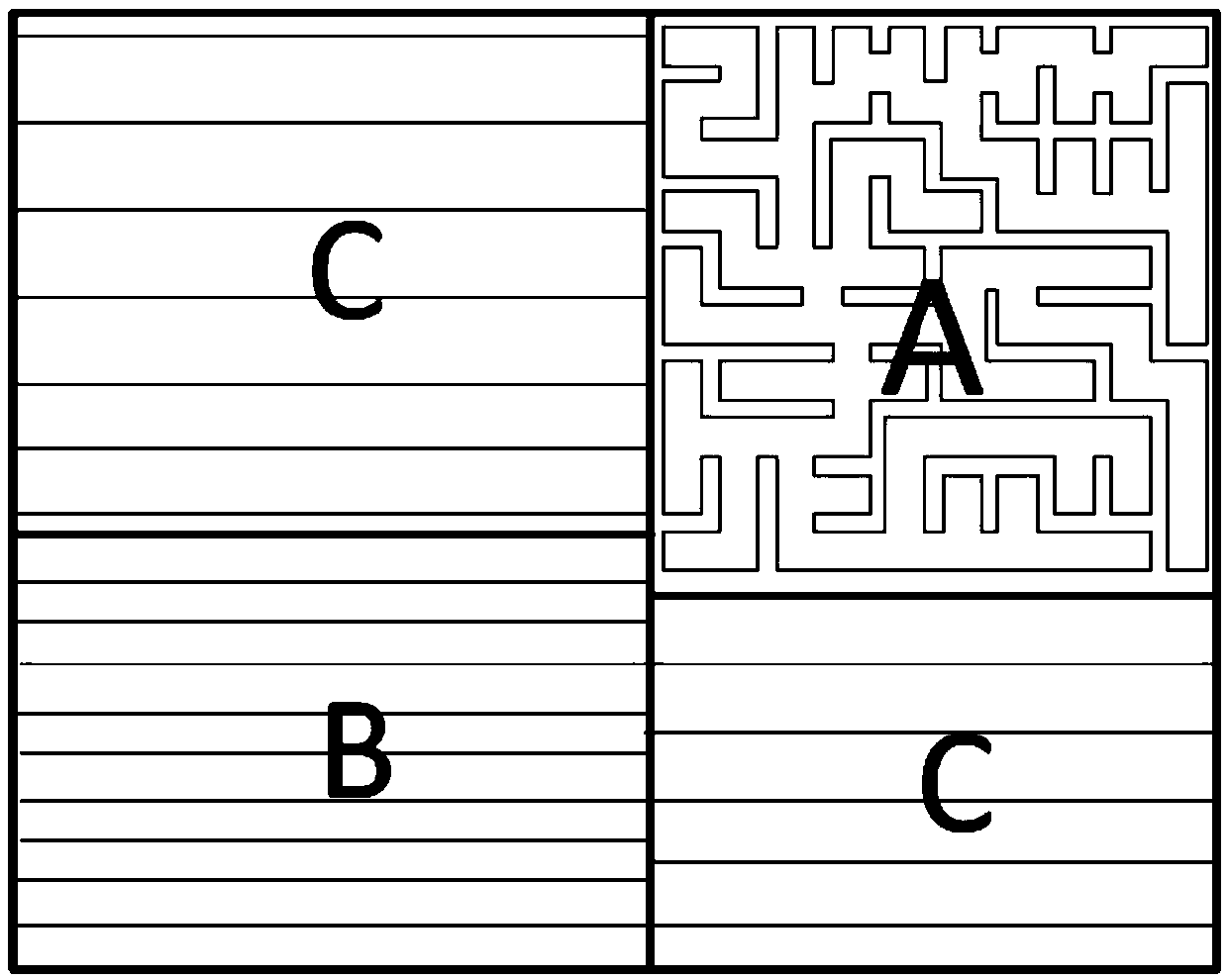

[0022] According to the protection area and degree of protection required by the chip module, the entire wiring layer is divided into multiple wiring areas. figure 1 It is a schematic diagram of the internal layout of a chip. The wiring area is divided into several types according to the security level of the internal structure of the chip, and the number of wiring lines is positively correlated with the security level of the area. Each routing area can be filled with serpentine routing, parallel routing, and random Hamiltonian loops. Among them, the random Hamiltonian circuit image has a high degree of disorder. It can reduce the ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More - R&D

- Intellectual Property

- Life Sciences

- Materials

- Tech Scout

- Unparalleled Data Quality

- Higher Quality Content

- 60% Fewer Hallucinations

Browse by: Latest US Patents, China's latest patents, Technical Efficacy Thesaurus, Application Domain, Technology Topic, Popular Technical Reports.

© 2025 PatSnap. All rights reserved.Legal|Privacy policy|Modern Slavery Act Transparency Statement|Sitemap|About US| Contact US: help@patsnap.com