An I2C-based RISC-V controller debugging method and device

A technology of RISC-V and debugging method, which is applied in the computer field, can solve the problems of direct monitoring and debugging of RISC-V controller chip BMC system, debugging RISC-V controller chip, etc., and achieve the effect of reducing the difficulty of debugging and speeding up the debugging speed

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0027] In order to make the object, technical solution and advantages of the present invention clearer, the embodiments of the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

[0028] It should be noted that all the expressions using "first" and "second" in the embodiments of the present invention are to distinguish two entities with the same name but different parameters or parameters that are not the same. It can be seen that "first" and "second " is only for the convenience of expression, and should not be understood as a limitation to the embodiments of the present invention, and will not be described one by one in the subsequent embodiments.

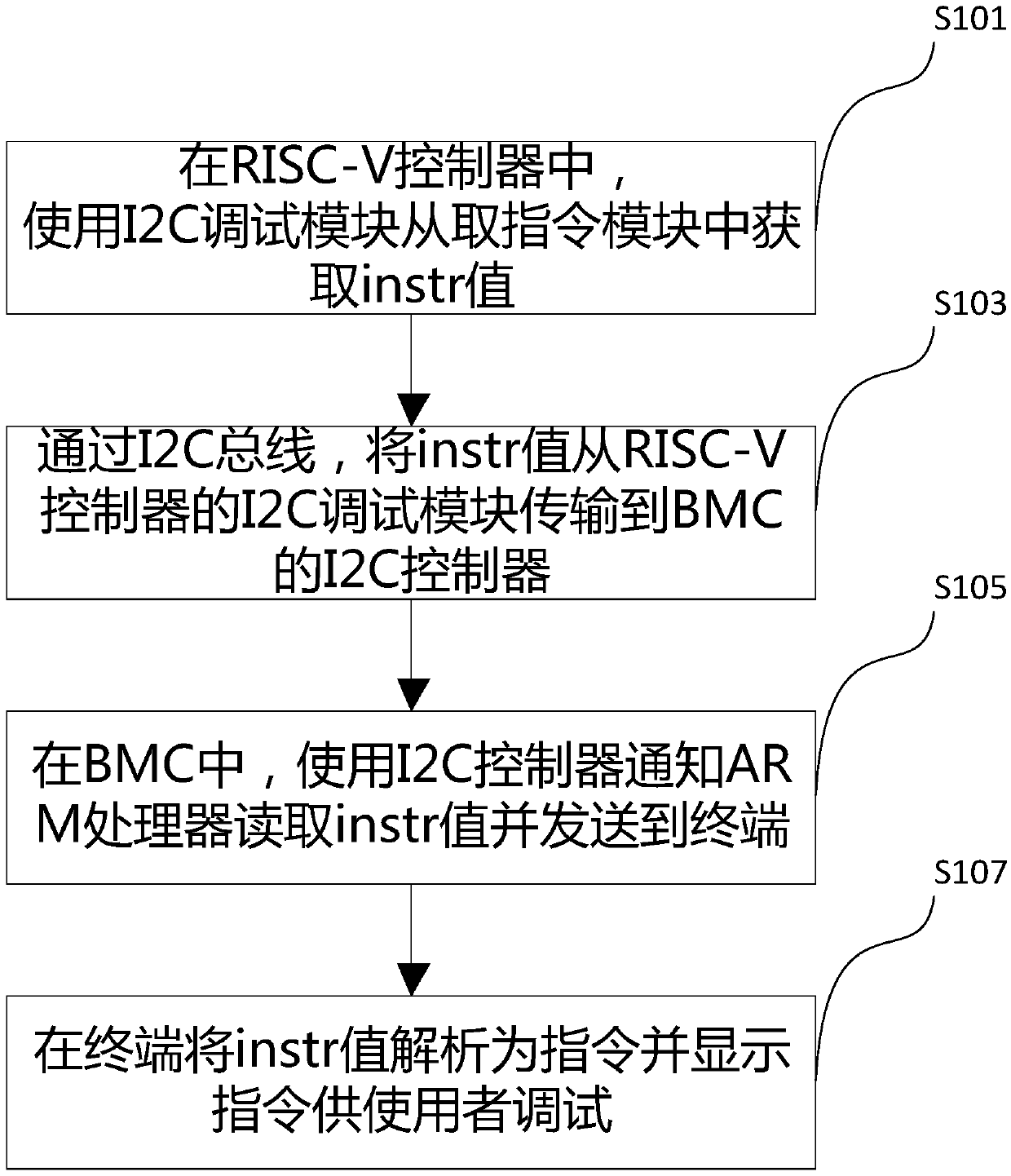

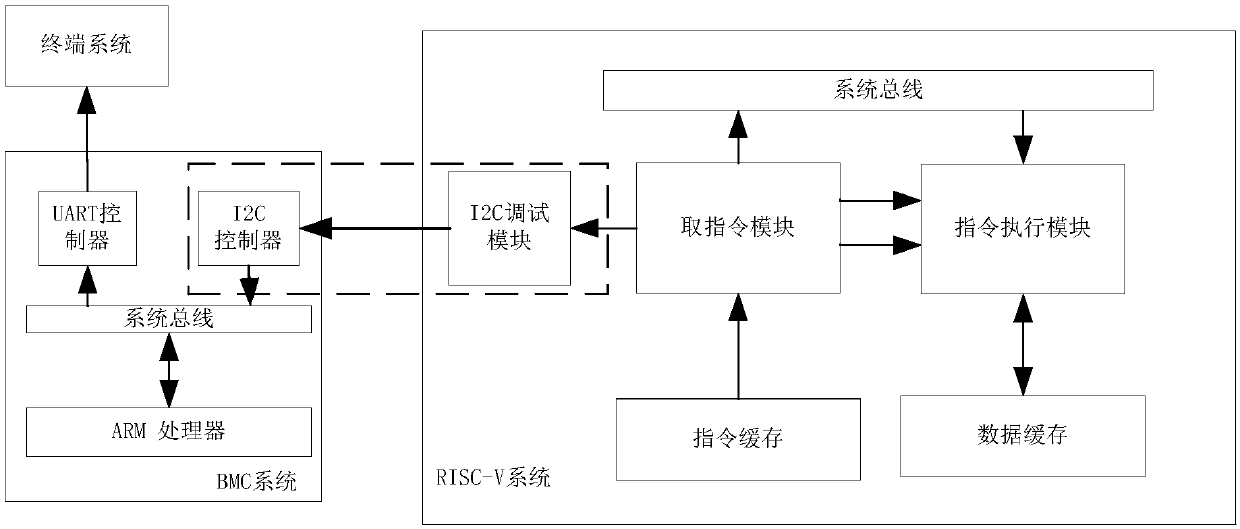

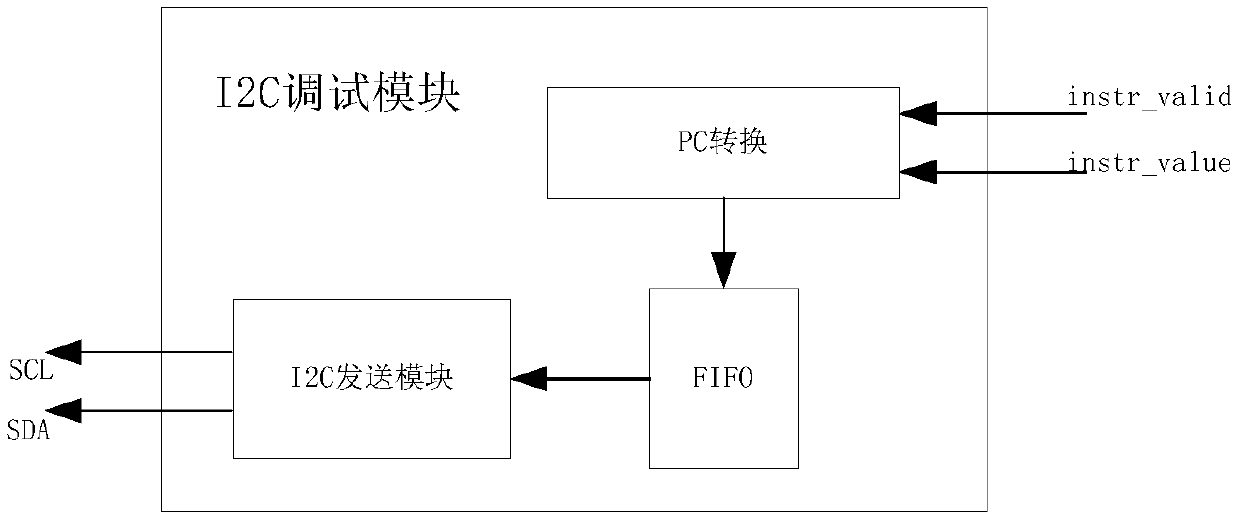

[0029] Based on the above purpose, the first aspect of the embodiments of the present invention proposes an embodiment of a monitoring and debugging method for different RISC-V controller chips or different types of RISC-V controller...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More