A high-level verification method applying a UVM verification platform

A verification platform and verification method technology, applied in special data processing applications, instruments, electrical digital data processing, etc., can solve the problem that UVM is difficult to handle data transmission and synchronization, verification complexity and error probability increase, and it is difficult to use and correct. Understanding and other issues to achieve the effect of improving data processing capabilities, simple and easy verification work, transparent and efficient verification environment

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

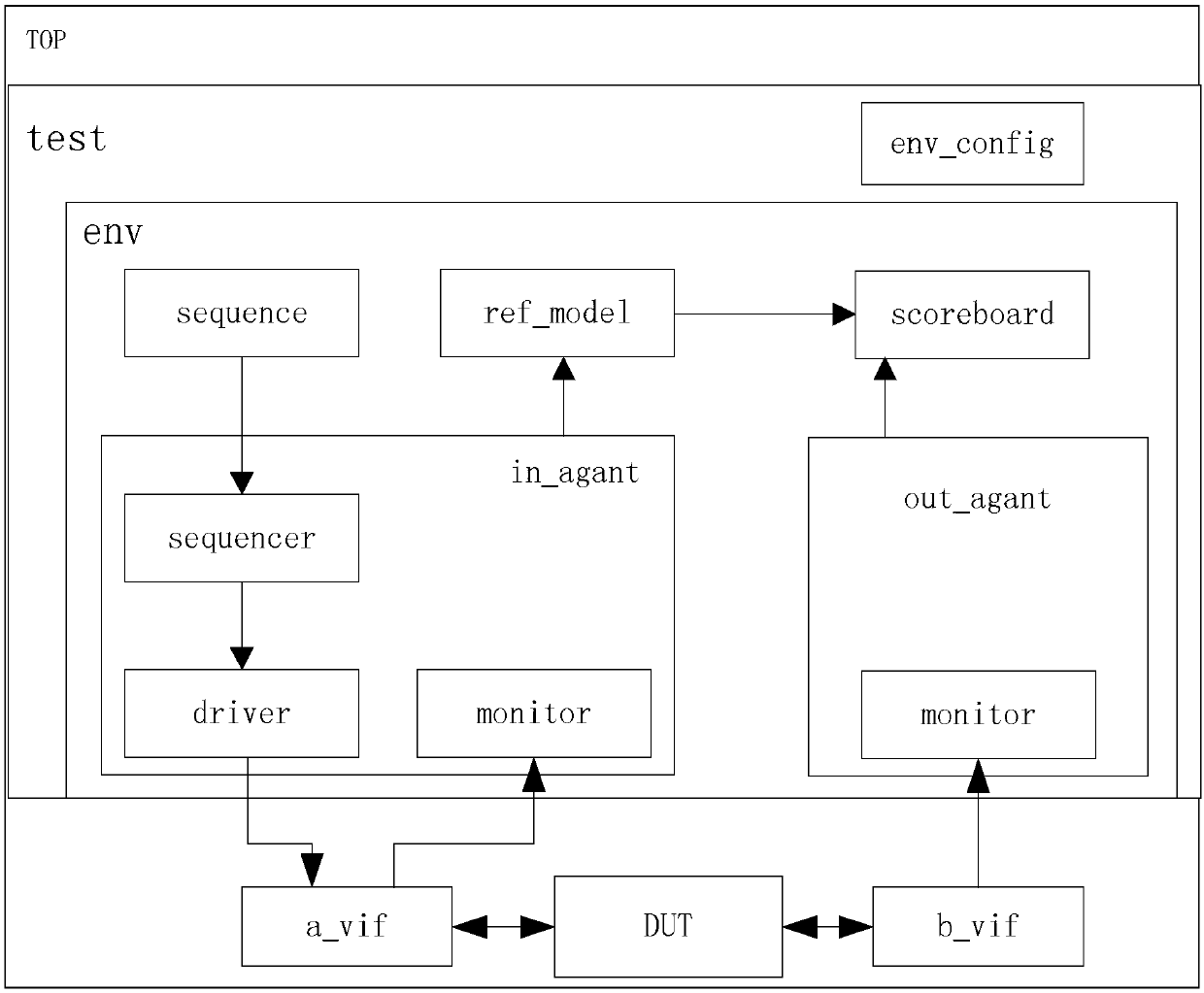

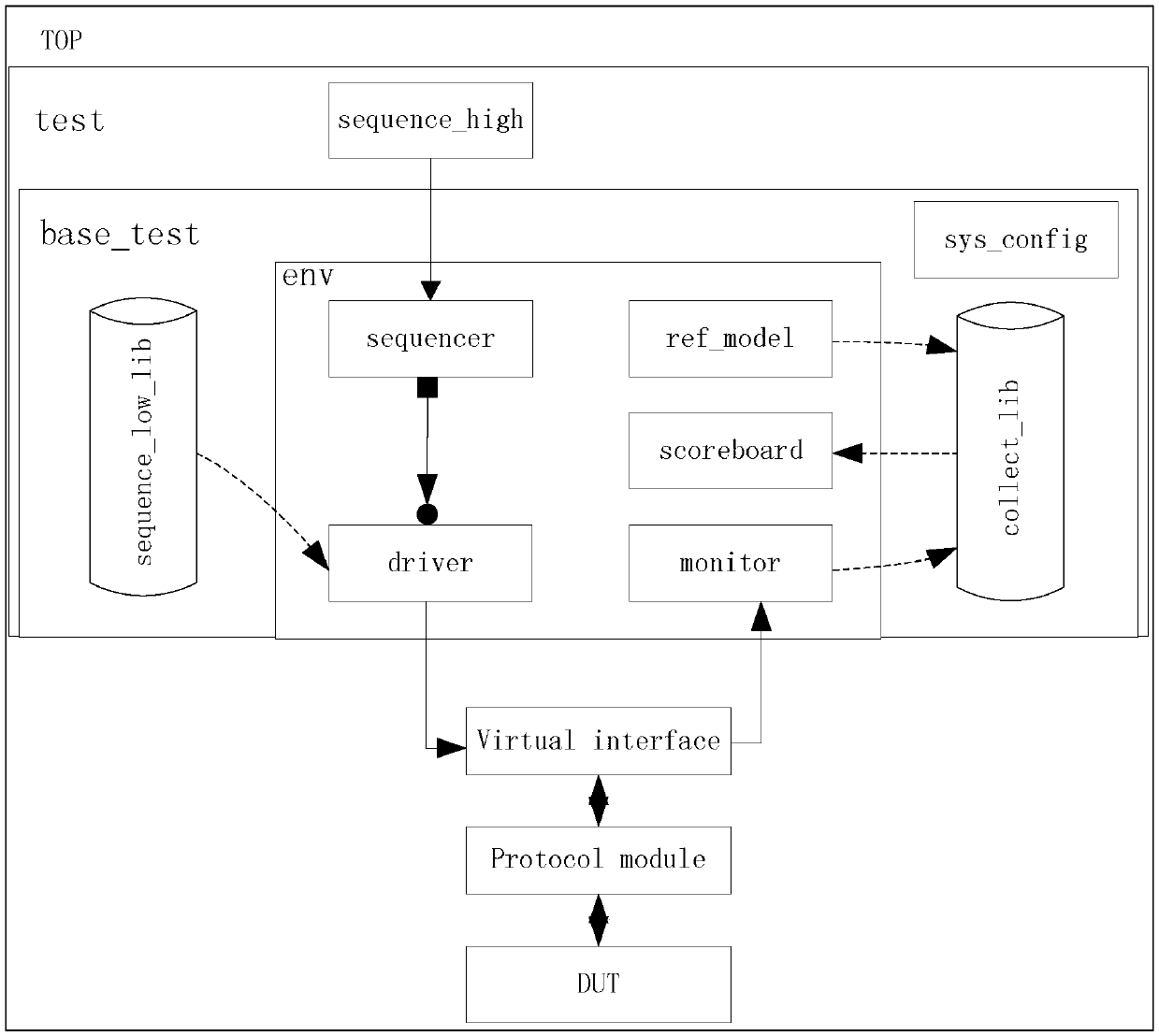

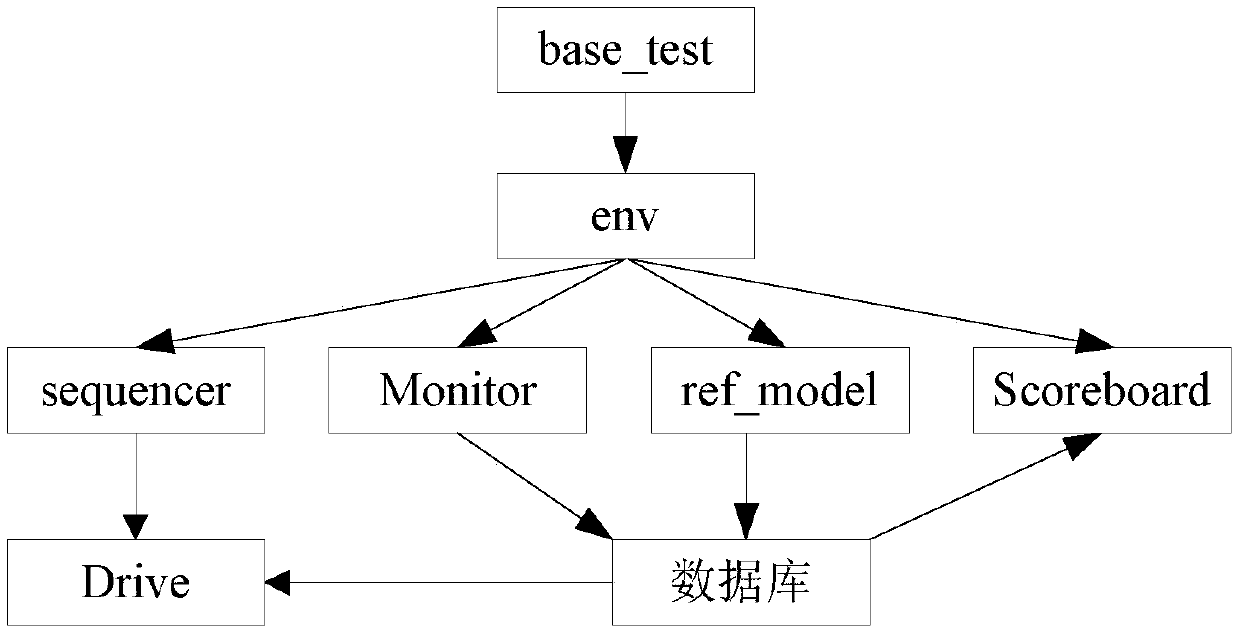

[0026] refer to figure 1 . According to the present invention, according to the universal UVM verification methodology, the UVM verification platform is divided into the topmost TOP layer, the TEST layer as the test layer, the BASE_TEST layer as the basic test layer, and the ENV layer as the environment layer in the programmable logic device FPGA. , the Interface layer as the interface layer and the DUT layer as the module to be verified, a total of six levels. The ENV layer is further divided into agent layer Agent, sequence Sequence, reference model Ref_model, and scoreboard Scoreboard. The agent layer Agent consists of three components: Sequencer, Driver, and Monitor. The BASE_TEST test layer is not displayed in the general platform and is only used as an auxiliary layer. The TOP layer is the top layer of the test platform. At the beginning, this layer is first called, mainly to complete the clock and reset signal generation required by the platform, and instantiate all i...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More