A compact nested inductor structure based on through-silicon vias and its preparation method

A technology of through-silicon vias and nesting, which is applied in the field of compact nested inductance structures based on through-silicon vias and its preparation, can solve problems such as increasing the inductance value, increasing the number of rings, and affecting integration density, so as to improve the inductance value , increase inductance density, reduce the effect of occupied area

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

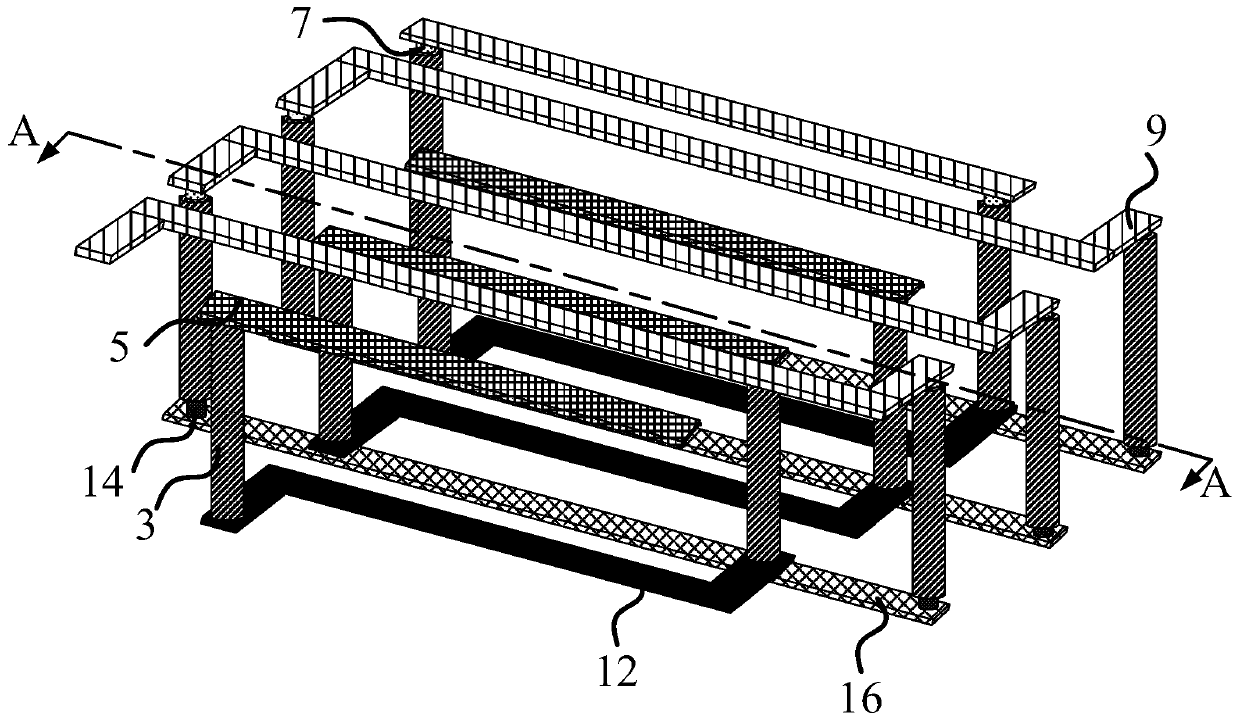

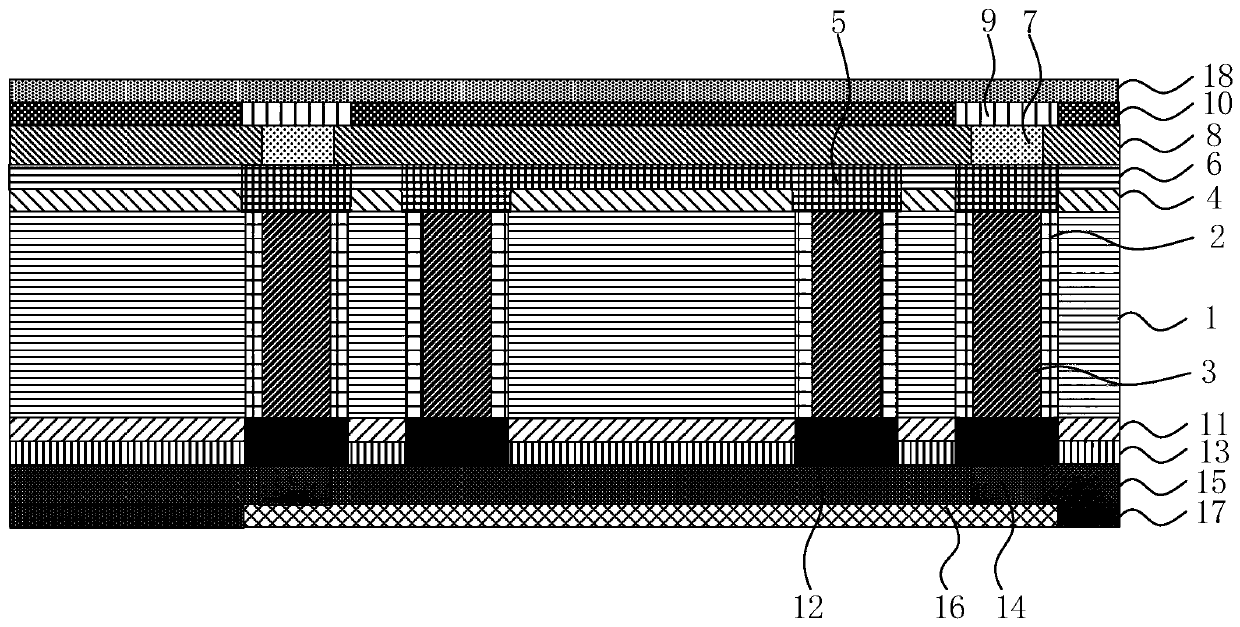

[0046] See also figure 1 and figure 2 , figure 1 A schematic structural diagram of a compact nested inductor structure based on through-silicon vias provided by an embodiment of the present invention; figure 2 for figure 1 Schematic diagram of the cross-sectional structure of AA in . It should be noted, figure 1 In order to better represent the compact nested inductance structure, only a structural schematic diagram of the metal part of the compact nested inductance structure is shown, the semiconductor substrate 1, the annular dielectric layer 2, the first isolation layer 4, the fourth isolation layer 8, The fifth isolation layer 10 , the second isolation layer 11 , the second isolation layer 11 , the sixth isolation layer 13 , the seventh isolation layer 15 , the eighth isolation layer 17 and the passivation layer 18 are not shown.

[0047] A TSV-based compact nested inductor structure comprising:

[0048] semiconductor substrate 1;

[0049] through-silicon vias loc...

Embodiment 2

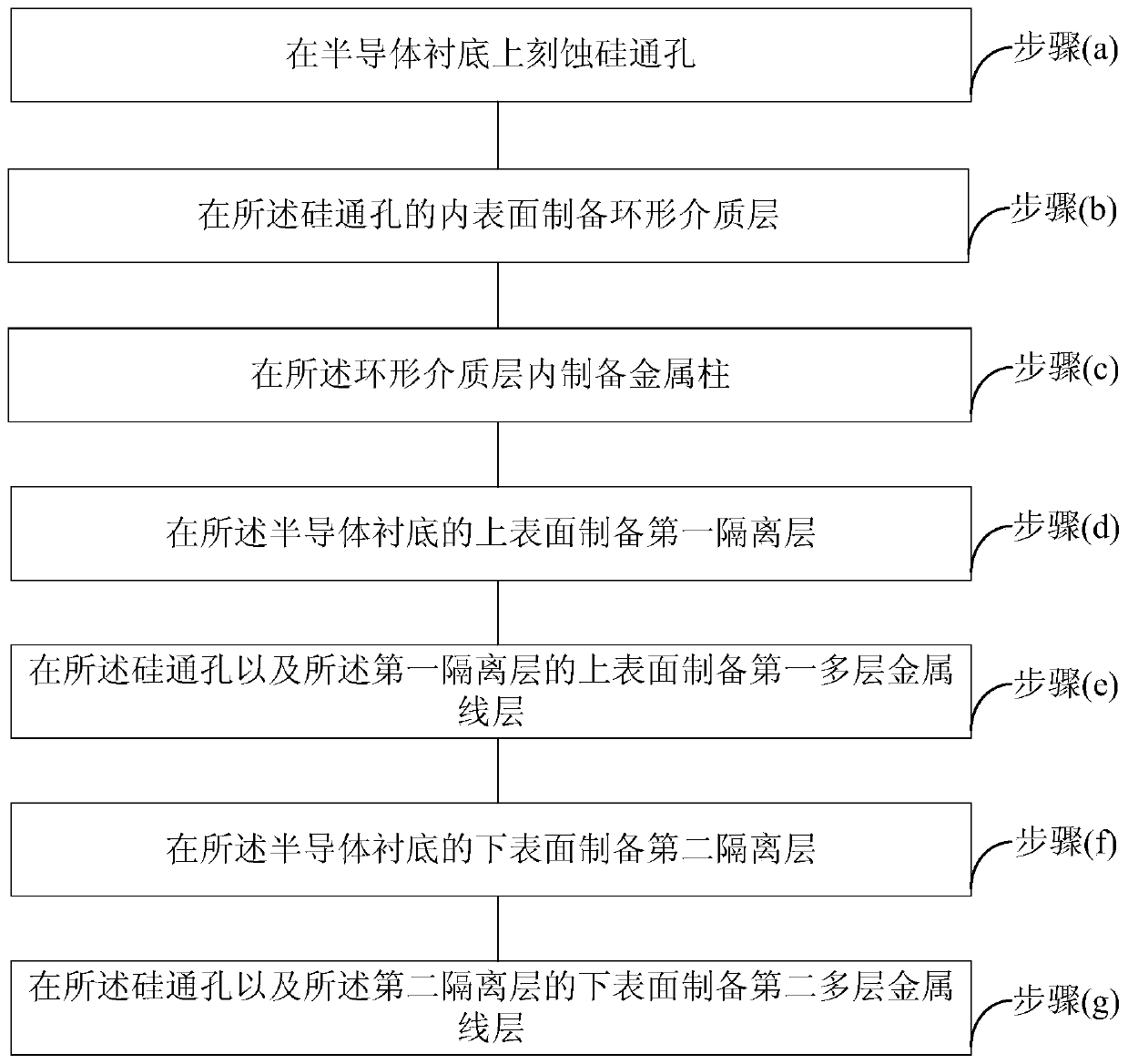

[0088] On the basis of the above-mentioned embodiments, this embodiment describes in detail a method for manufacturing a compact nested inductor structure based on TSVs.

[0089] See image 3 , image 3 A schematic flow chart of a method for preparing a compact nested inductor structure based on through-silicon vias provided by an embodiment of the present invention, the method includes the following steps:

[0090] Step a: Etching TSVs on the semiconductor substrate 1 .

[0091] Further, several through-silicon vias with a radius of 2.1-12 μm are etched on the semiconductor substrate 1 by reactive ion etching.

[0092] Step b: preparing an annular dielectric layer 2 on the inner surface of the TSV.

[0093] Further, an annular dielectric layer 2 with a thickness of 0.1-2 μm is prepared on the inner surface of the TSV. The function of the annular dielectric layer 2 is to realize electrical isolation between the semiconductor substrate 1 and the TSV, thereby reducing the imp...

Embodiment 3

[0126] see again figure 1 and figure 2 , the embodiment of the present invention provides another description of the compact nested inductor structure.

[0127] The compact nested inductor structure includes: a semiconductor substrate 1, through-silicon vias, an annular dielectric layer 2, metal pillars 3, a first isolation layer 4, a first metal line layer 5, a third isolation layer 6, and a first metal via Layer 7, the fourth isolation layer 8, the second metal line layer 9, the fifth isolation layer 10, the second isolation layer 11, the third metal line layer 12, the sixth isolation layer 13, the second metal via layer 14, the second The seventh isolation layer 15 , the fourth metal line layer 16 , the eighth isolation layer 17 , and the passivation layer 18 .

[0128] Wherein, the TSV is located inside the semiconductor substrate 1 , the metal pillar 3 is located inside the TSV, and the annular dielectric layer 3 is located between the metal pillar 4 and the TSV.

[0...

PUM

| Property | Measurement | Unit |

|---|---|---|

| radius | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

| thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More