Termination design for trench superjunction power MOSFET

A trench and termination technology, applied in semiconductor devices, electrical components, circuits, etc., can solve problems such as large on-state resistance of FETs

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

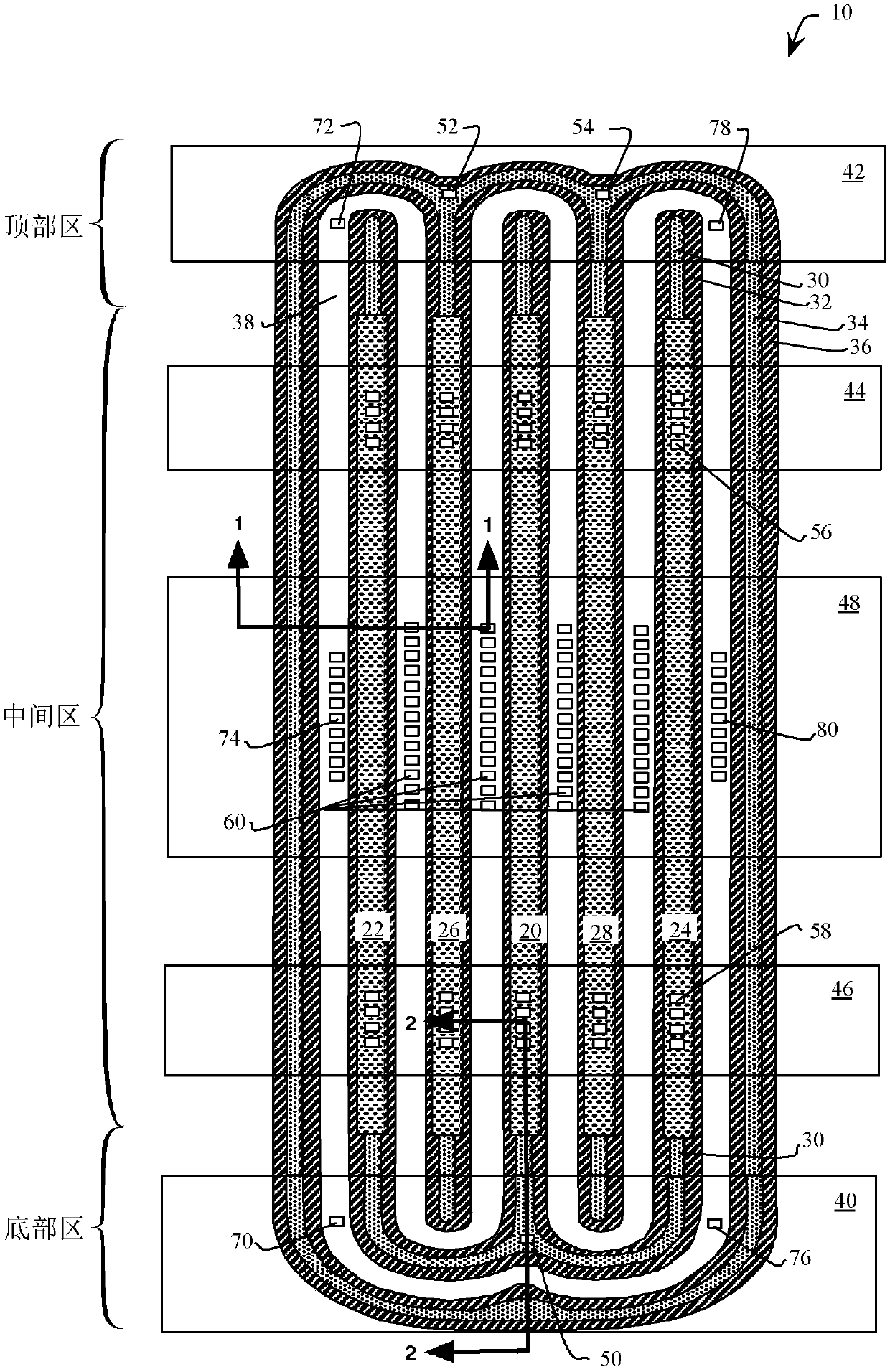

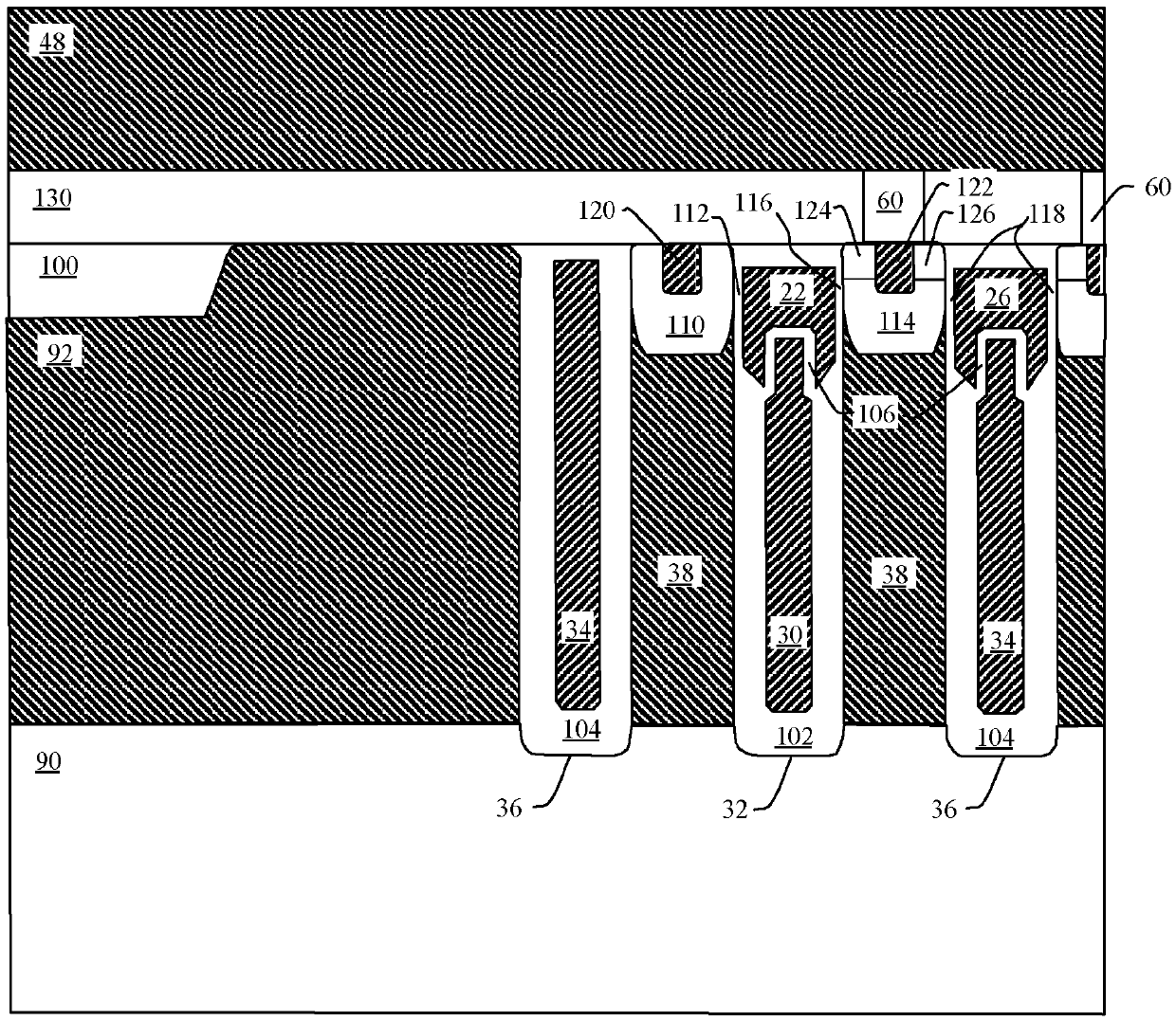

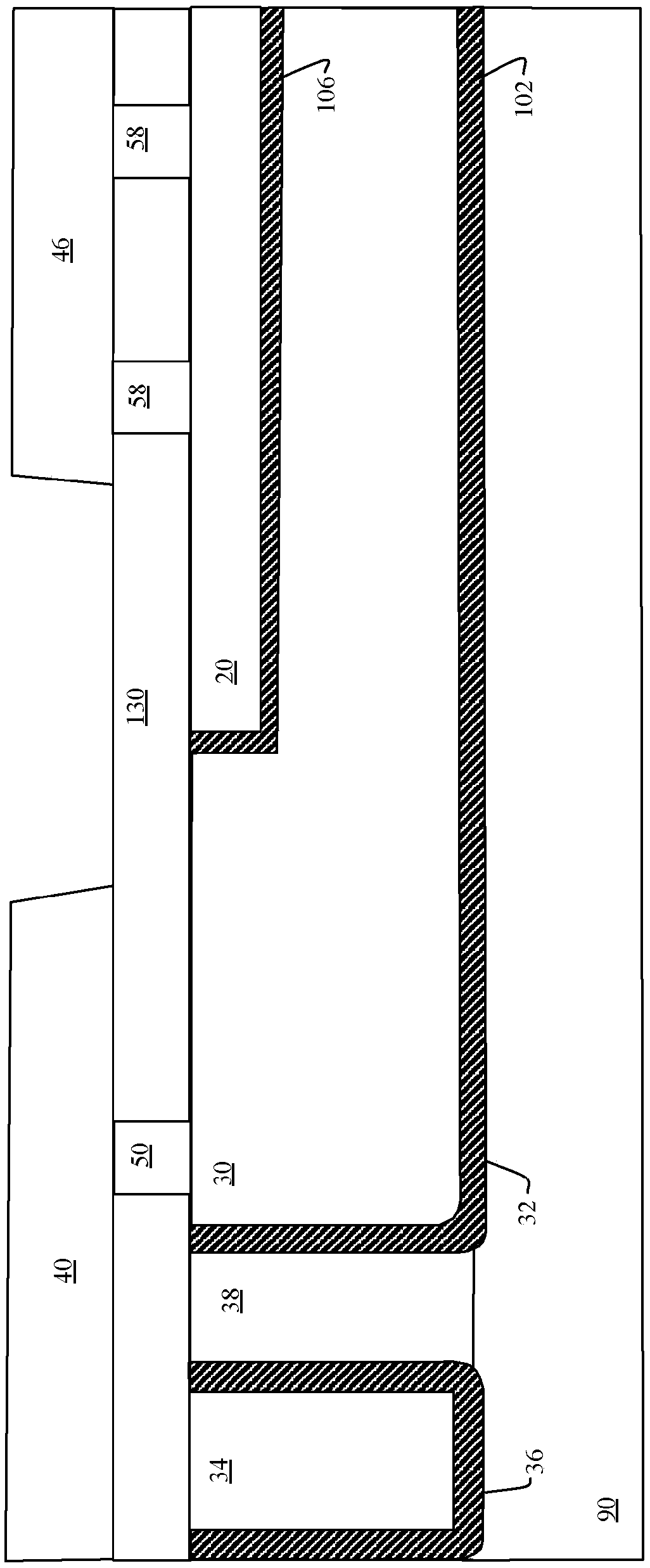

[0056] Embodiments of the systems and methods described herein provide improved voltage breakdown characteristics by rotating silicon mesas around gate trench fingers rather than using conventional methods of rotating gate trenches around silicon mesa fingers . In various embodiments, contacts to the shields formed under the gate trenches are made at "triple point" locations defined by the intersection of the three trenches comprising the shields. Contact shielding at triple point locations improves shielding overlap of contacts and synergizes with improved layout using silicon mesas that rotate around gate trench fingers. Advantageously, the triple point contact and layout embodiments of the present disclosure enable the use of a single metal fabrication process to reduce cost and complexity, in addition to improved layout density.

[0057] Furthermore, the disclosed trench layout embodiments enable an optimized doping concentration of the epitaxial layer to improve the volt...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More