A bridging method for ahb bus to access on-chip sram

A bus and bridging technology, applied in the bridging field of AHB bus access to on-chip SRAM, can solve the problem of low timing efficiency, and achieve the effects of optimizing timing, improving data transmission efficiency and improving efficiency

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

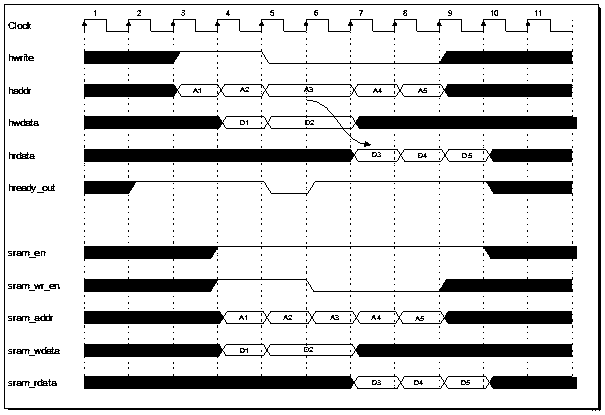

[0021] The technical solution of the present invention will be further described below in conjunction with the accompanying drawings.

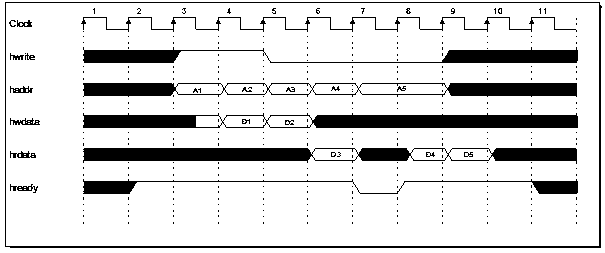

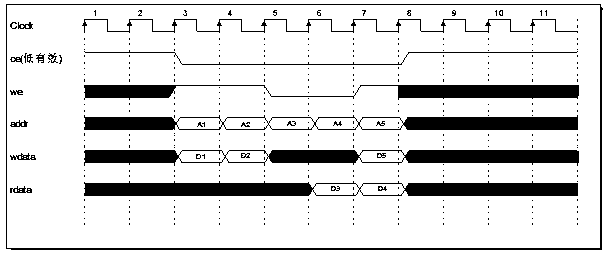

[0022] The method proposed in this patent is a bridge method for AHB bus to access on-chip SRAM. The characteristics of this method are: during the read operation, since the timing of the AHB is the same as that of the SRAM, so in the case of only a read operation in a section of transmission, the control signal of the AHB terminal can be directly connected with the control signal of the SRAM terminal, and the data signal of the AHB terminal can be connected with the control signal of the SRAM terminal. The data signal at the SRAM end is directly connected; during the write operation, since the timing of AHB is to initiate the control signal in the previous beat, and then transmit the data in the next beat, and the timing of the SRAM is that the control signal and the write data are accepted in the same cycle, so in a period of transmission In...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More