Buffer interface circuit and method and application for transmitting data based on circuit

A technology of interface circuit and buffer, which is applied in the field of buffer interface circuit, can solve the problem of low buffer access efficiency and achieve the effect of realizing, improving data interaction efficiency, and high-efficiency data interaction

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0050] The present invention will be further described in detail below in conjunction with specific embodiments, which are explanations of the present invention rather than limitations.

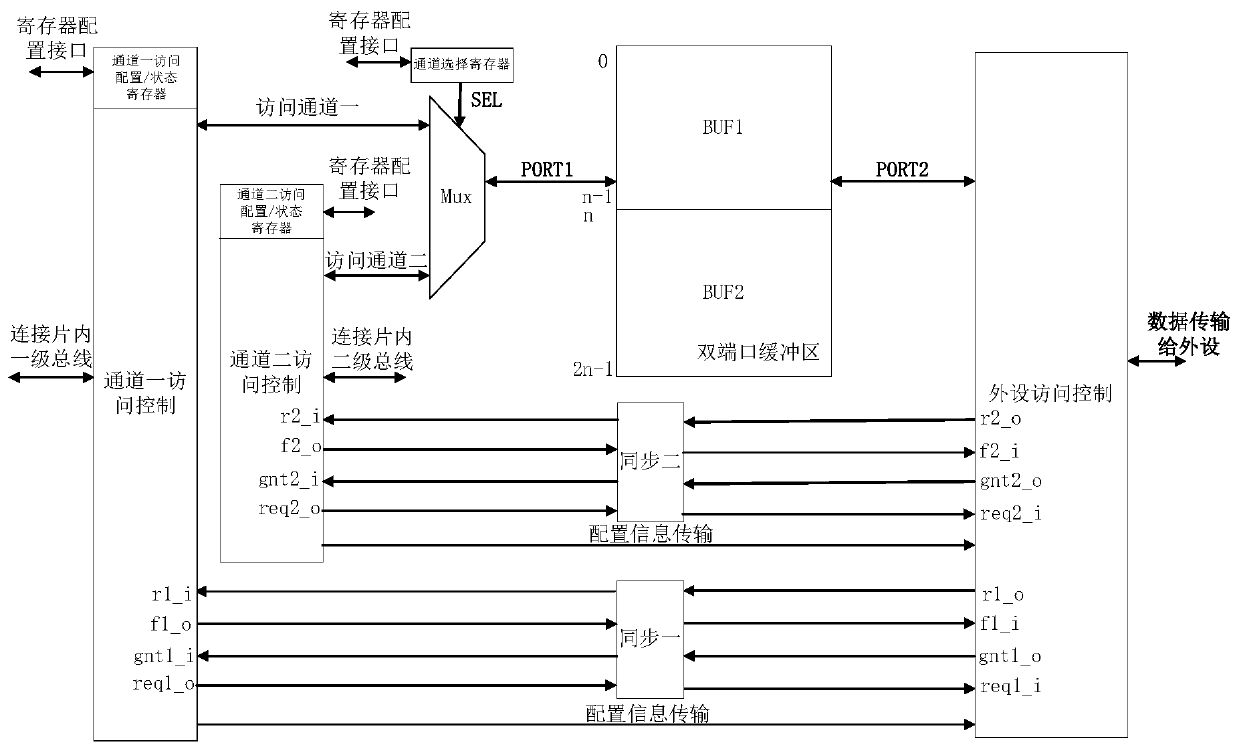

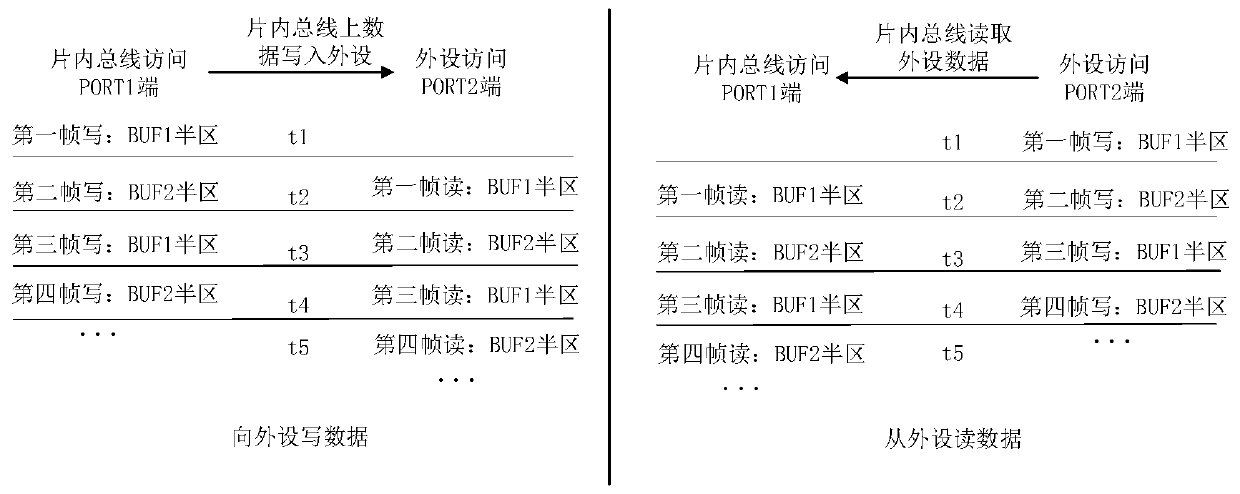

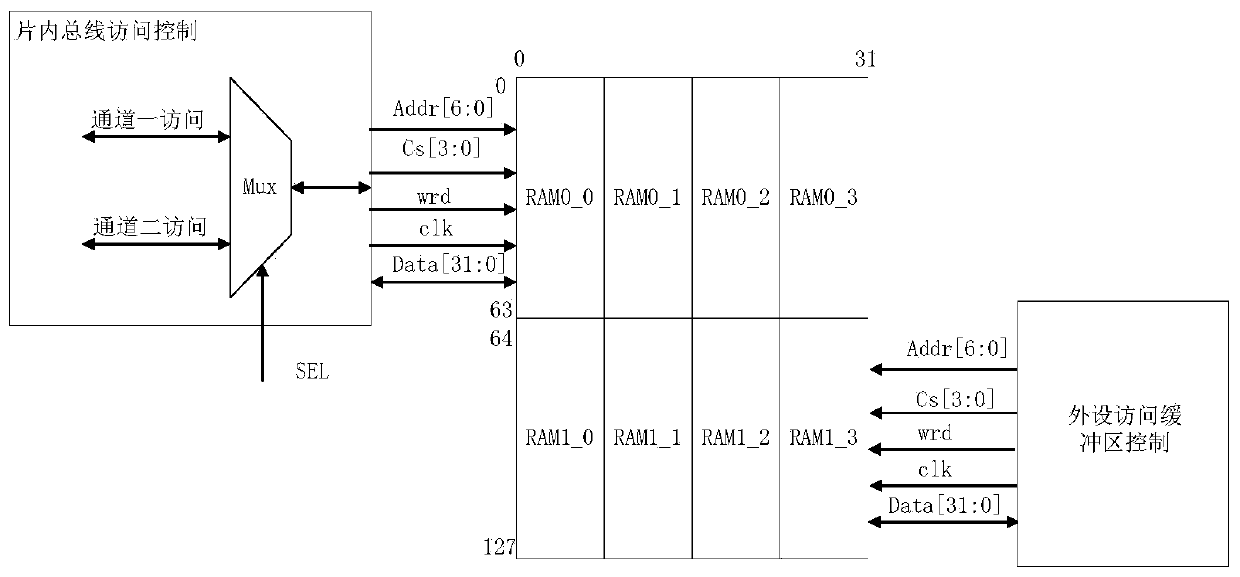

[0051] Such as figure 1 As shown, the buffer interface circuit of the present invention is a high-speed buffer interface circuit based on two-stage pipeline control across multiple clock domains, including a channel-one access control module, a channel-two access control module, a MUX unit, and a synchronization module , Synchronous second module, dual-port buffer and peripheral access buffer control module.

[0052] One end of the channel-one access control module is connected to the on-chip first-level bus, and the other end is connected to the dual-port buffer after being selected by the MUX unit. At the same time, the channel-one access control module exchanges control information with the peripheral access buffer control module by synchronizing the first module. One end of the channel t...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More