How nldmos is made

A manufacturing method and body region technology, applied in the direction of semiconductor/solid-state device manufacturing, semiconductor devices, electrical components, etc., can solve the problems of SLDMOS failure and inability to form a channel, and achieve the effect of preventing channel failure and device failure.

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

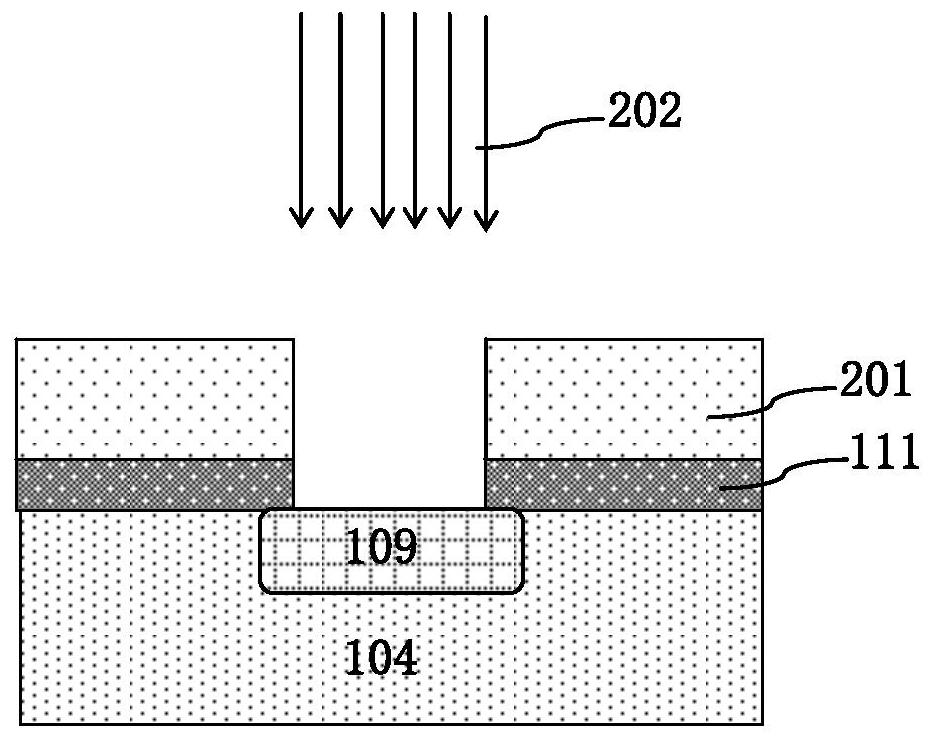

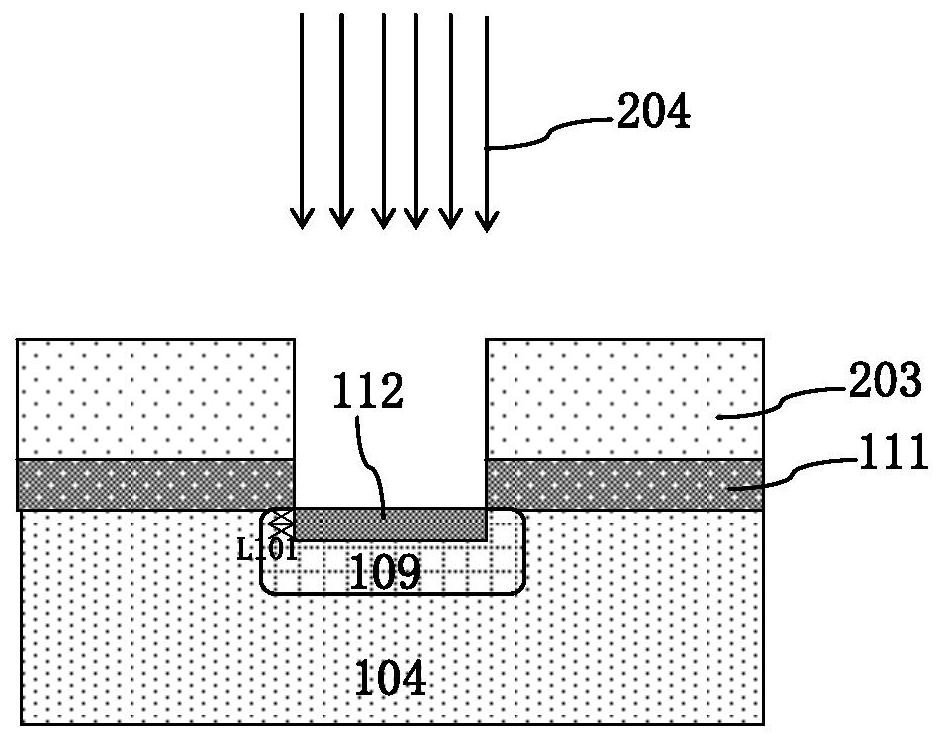

[0058] Such as image 3 Shown is the flow chart of the method of the embodiment of the present invention; Figure 4A to Figure 4D As shown, it is a device structure diagram in the step of forming the P-type body region 109 in the method of the embodiment of the present invention. In the manufacturing method of NLDMOS in the embodiment of the present invention:

[0059] In the manufacturing method of the NLDMOS of the embodiment of the present invention:

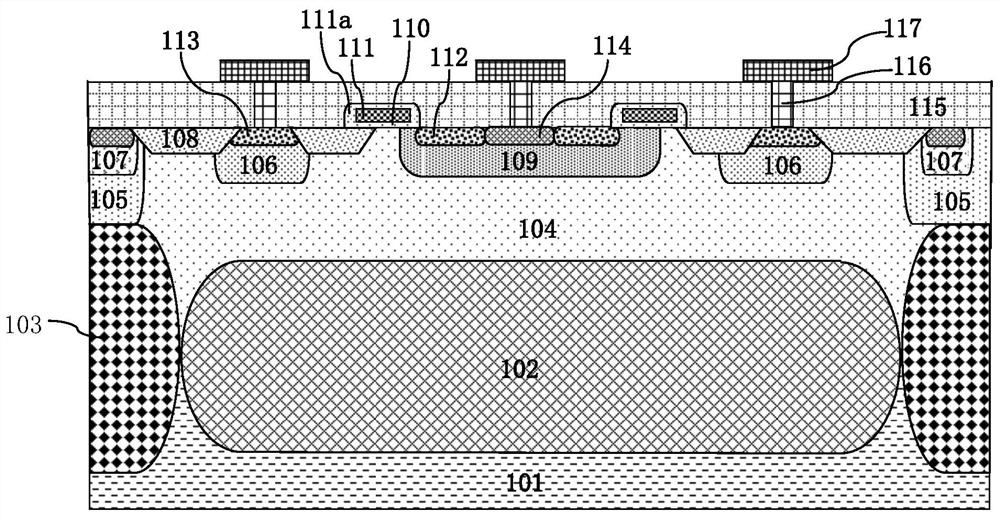

[0060] First, form a deep N well 104, a low voltage N well 106, a field oxygen isolation layer 108 on the semiconductor substrate such as a silicon substrate 101, and deposit a gate dielectric layer such as a gate oxide layer 110 and The polysilicon gate 111 specifically includes: after forming an N-type buried layer 102 and a P-type buried layer 103 on the silicon substrate 101, a deep N well 104 is defined, and the deep N well 104 is formed by N-type implantation and annealing. After that, the field oxygen isolation layer...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More