Word line ladder lifting device and method for relieving reading disturbance by using word line ladder lifting device

A read disturbance and ladder lifter technology, applied in instruments, static memory, read-only memory, etc., can solve problems such as reducing write capability, reduce instability, avoid low yield, and reduce read disturbance Effect

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

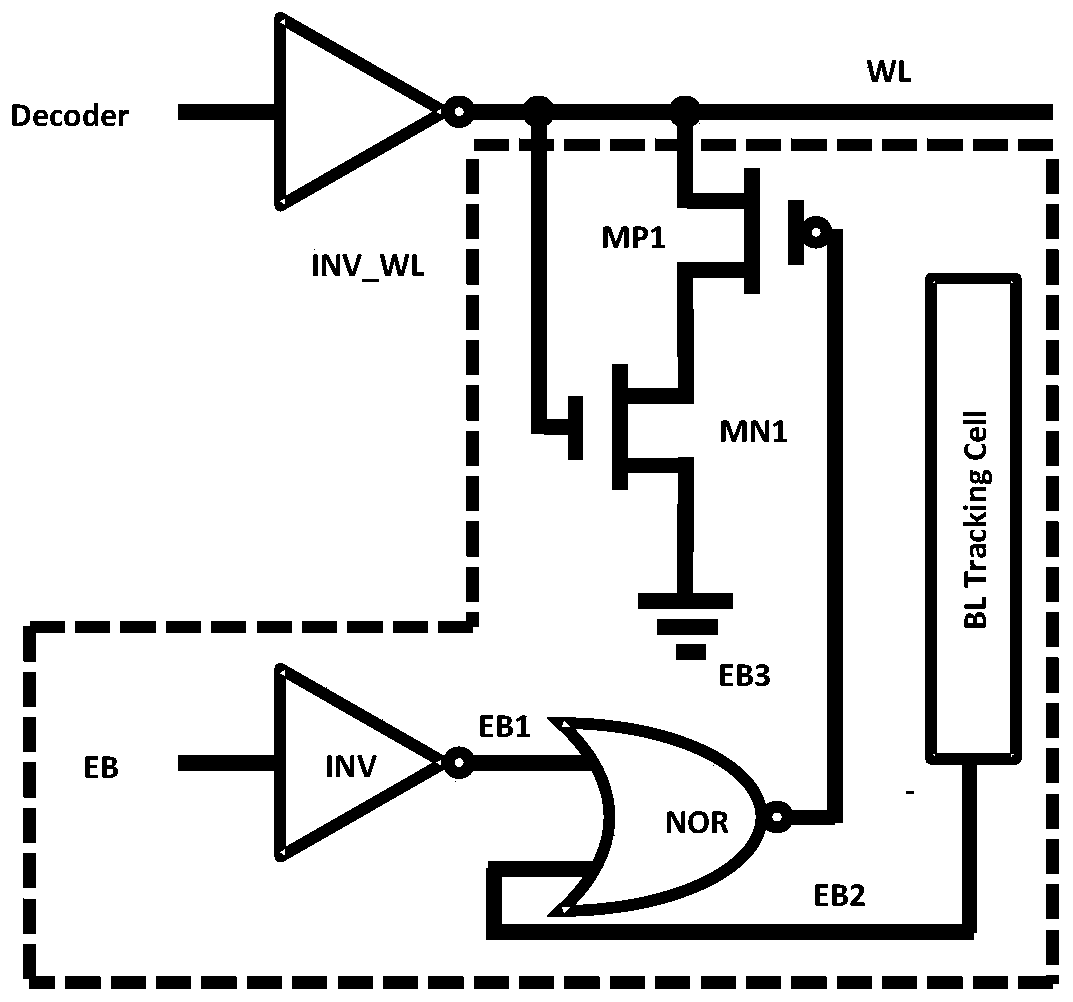

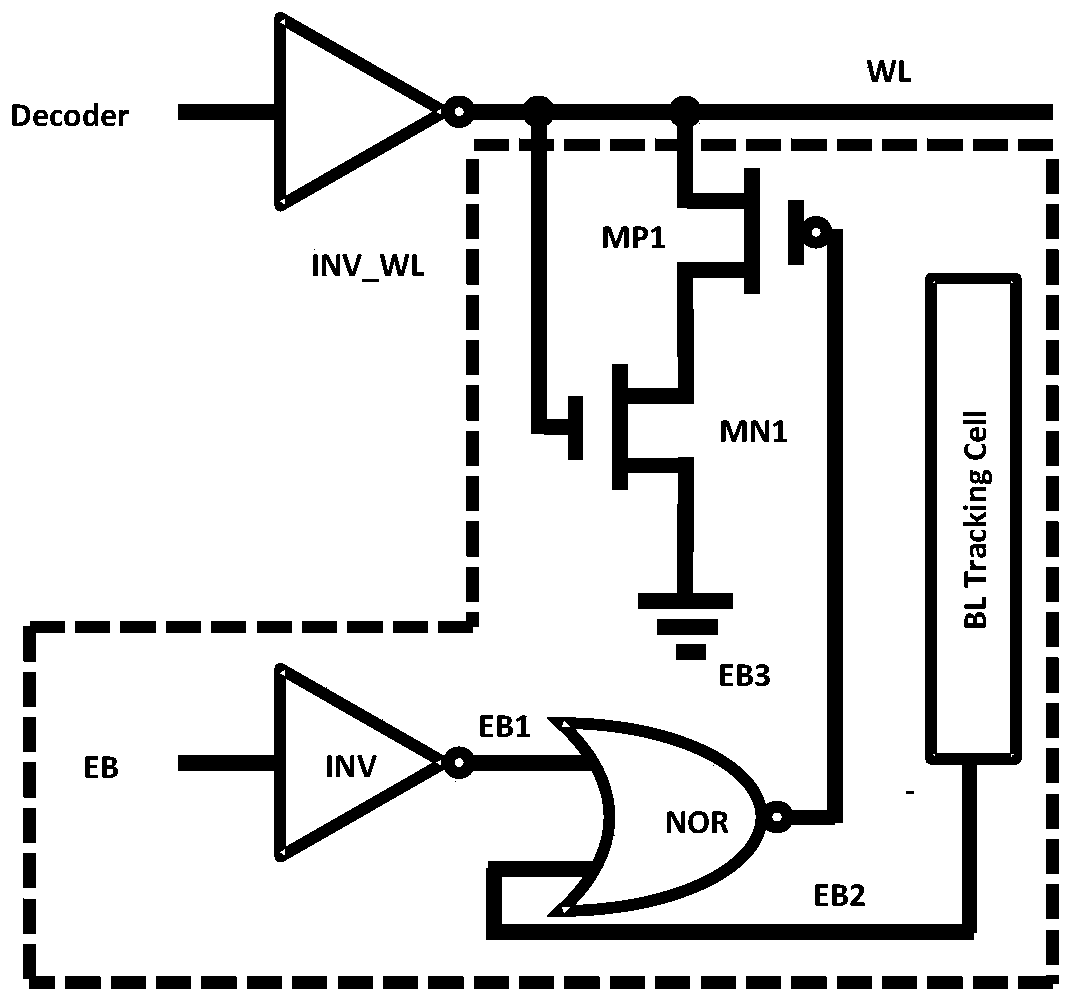

[0022] Such as figure 1 as shown, figure 1 Shown is a schematic circuit diagram of the word line lifter of the present invention. This embodiment provides a word line lifter, the word line lifter includes: an inverter INV_WL, a PMOS transistor MP1 and an NMOS transistor MN1; the input terminal of the inverter INV_WL is connected to an input signal, and its output terminal, The source of the PMOS transistor MP1 and the gate of the NMOS transistor MN1 are connected to the word line WL; the drain of the PMOS transistor MP1 is connected to the drain of the NMOS transistor MN1, and the source of the NMOS transistor MN1 Grounding; In this embodiment of the present invention, preferably, the word line lifter also includes figure 1 As shown in the decoder (decoder), the input signal connected to the input terminal of the inverter INV_WL is provided by the decoder. That is to say, the decoded signal is given by the decoder. After the decoded signal passes through the inverter INV_WL...

Embodiment 2

[0034] After carrying out the three steps of Embodiment 1, through the selection of the number of bit line tracking units, the working stability of the elevators corresponding to different numbers of bit line tracking units can be compared, and the reading disturbance can be reduced and semi-selective interference. In this embodiment, without changing the number of bit line tracking units, an external signal is input to the lifter to adjust the working stability of the lifter and reduce read disturbance and half selection disturbance.

[0035] The steps in this embodiment may be supplemented after performing the three steps in the first embodiment. It can also be implemented independently. Here, it is preferable to perform step 4, selecting the number of bit line tracking units after performing the three steps in Embodiment 1. Preferably, the number of units of the bit line tracking unit ranges from 8 to 512. Further, the number of selected bit line tracking units is 16, 64 ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More