Field-effect transistor fabrication method and field-effect transistor

A field effect transistor, two-dimensional semiconductor technology, applied in transistors, semiconductor/solid-state device manufacturing, semiconductor devices, etc., can solve the problems of too small output resistance, large source-drain voltage, stagnation of low-dimensional semiconductor applications, etc. The effect of operating voltage and power consumption, low cost, and simple structure

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment Construction

[0040] In order to make the object, technical solution and advantages of the present invention clearer, the present invention will be further described in detail below in conjunction with specific embodiments and with reference to the accompanying drawings.

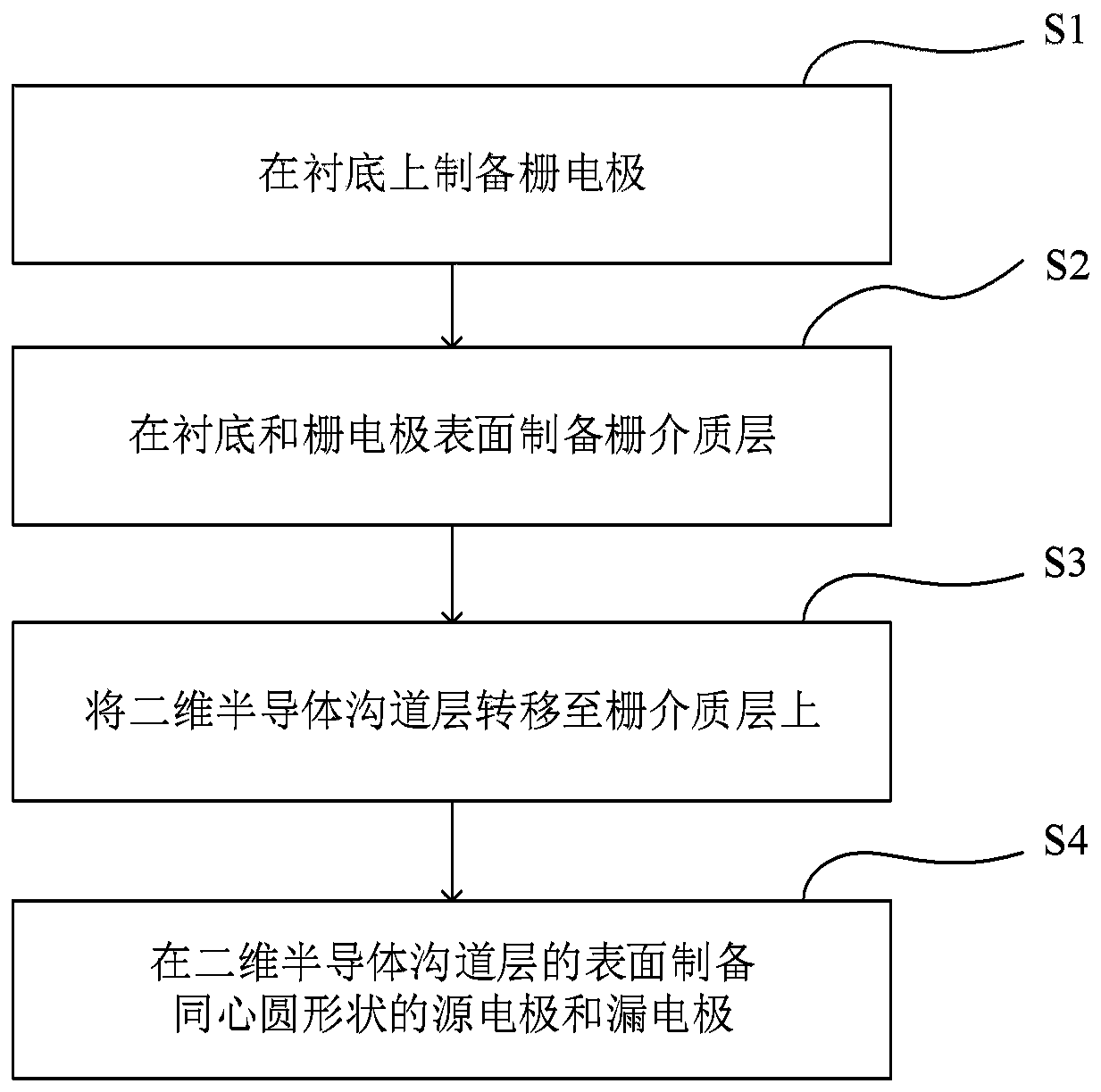

[0041] According to one aspect of the present invention, a kind of field effect transistor preparation method is provided, such as figure 1 As shown, the method includes the following steps:

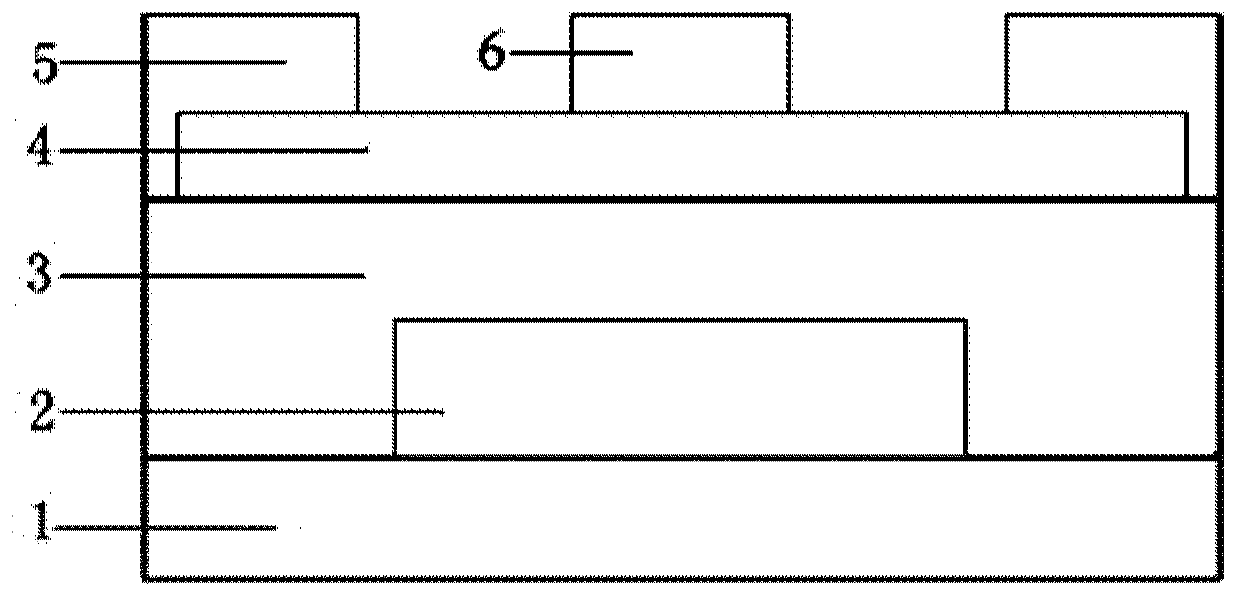

[0042] Step S1, preparing a gate electrode on the substrate;

[0043] Step S2, preparing a gate dielectric layer on the surface of the substrate and the gate electrode;

[0044] Step S3, transferring the two-dimensional semiconductor channel layer onto the gate dielectric layer;

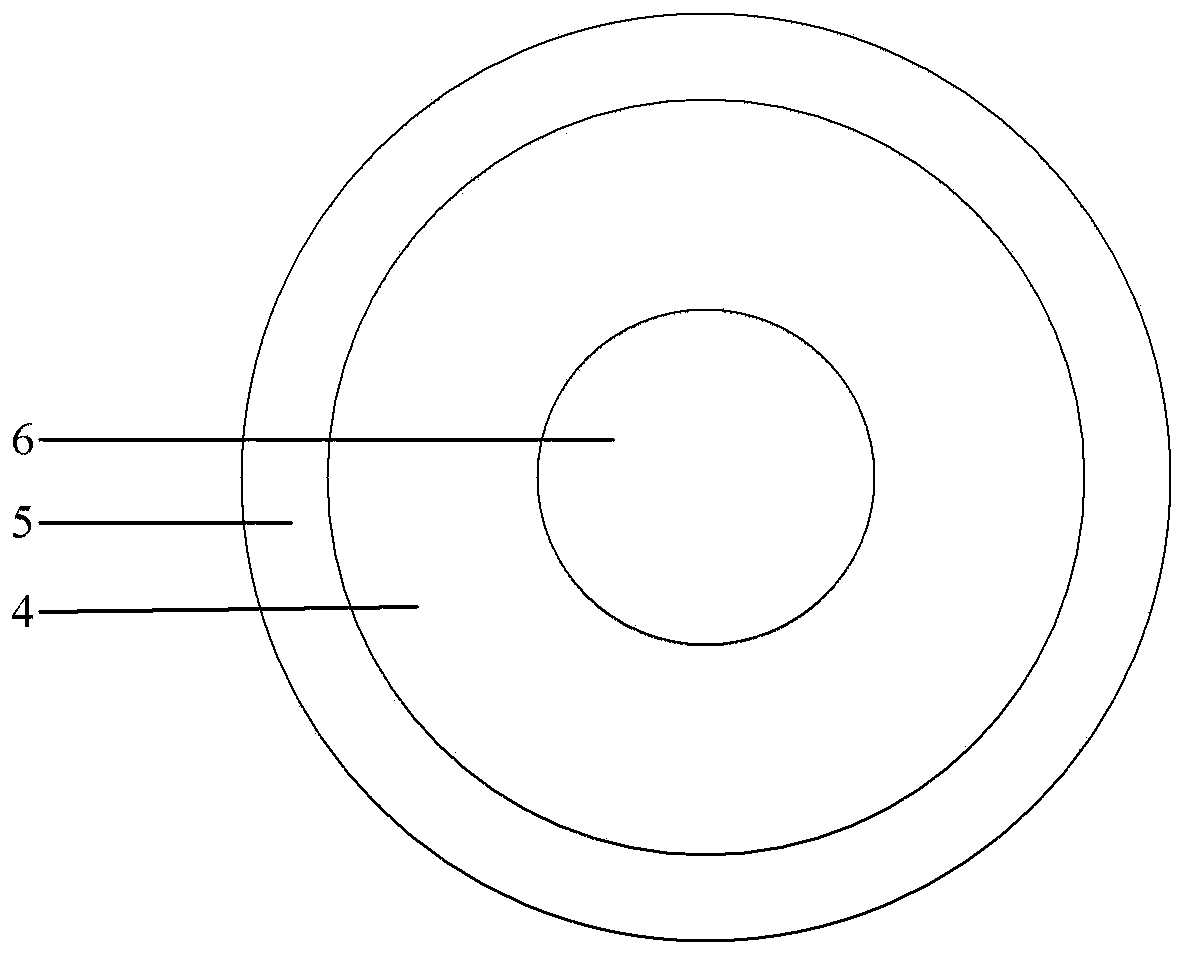

[0045] Step S4, preparing concentric circle-shaped source electrodes and drain electrodes on the surface of the two-dimensional semiconductor channel layer; wherein, the outer circle is the drain electrode, and the inner circle is the source electrode. ...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More