Decoding method of ldpc code based on dynamic block update of variable nodes

An LDPC code and variable node technology, applied in the field of LDPC code decoding, can solve the problem that it is difficult to meet the error correction performance requirements of NAND-Flash

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment

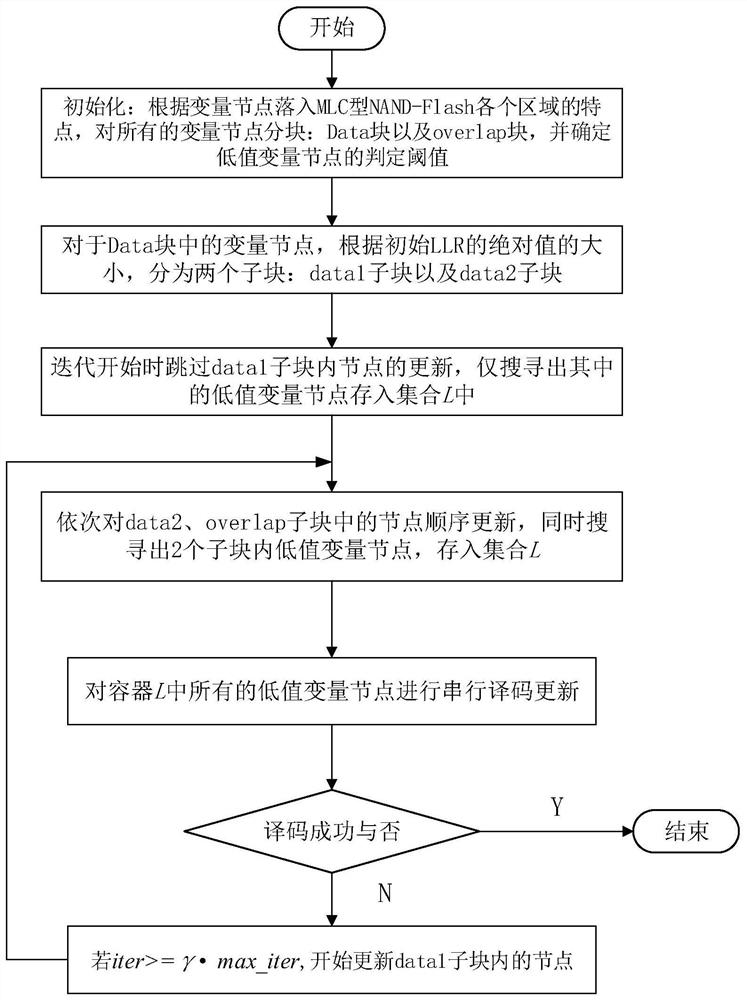

[0063] Such as figure 1 , figure 2 As shown, this embodiment provides an LDPC code decoding method based on variable node dynamic block for MLC type NAND-Flash, including the following steps:

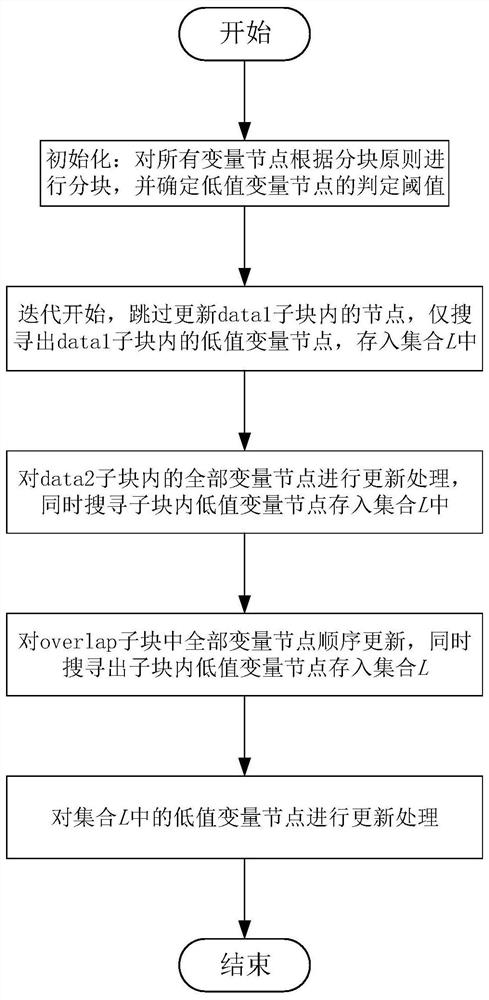

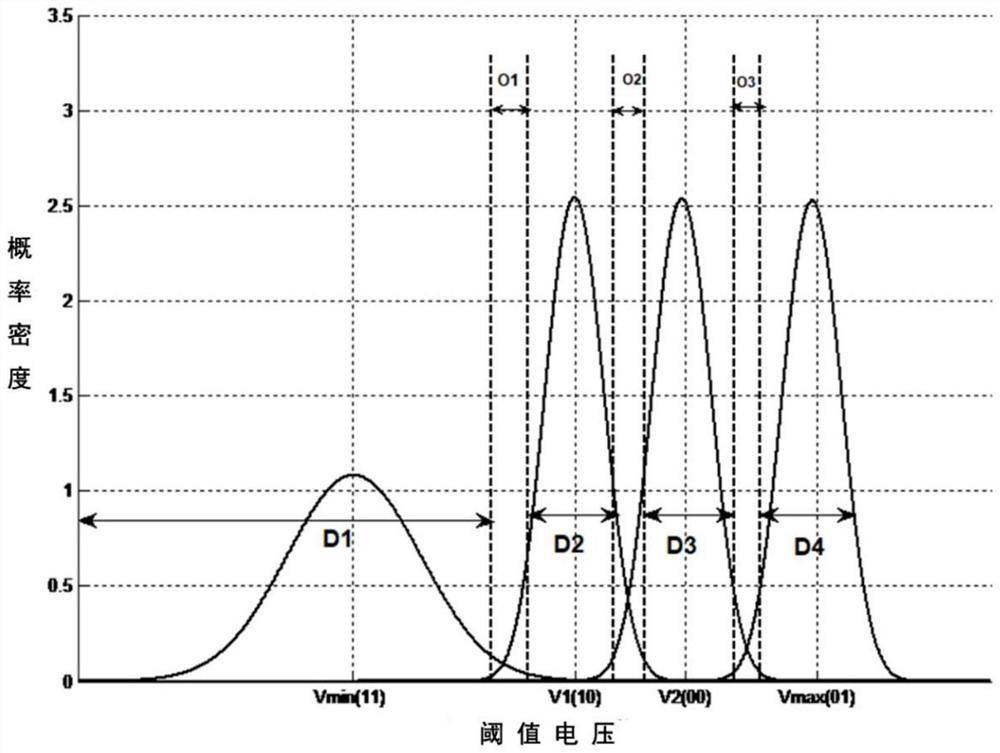

[0064] S1. In the NAND-Flash storage channel, all variable nodes are divided into blocks according to the probability that the voltage of the variable node falls into each area: the variable nodes in the non-overlapping area are divided into Data blocks, and the variable nodes in the overlapping area are divided into Divided into overlapping sub-blocks;

[0065] S2. Continue subdividing each sub-block into a plurality of sub-blocks according to the absolute value of the variable node initial LLR value in each sub-block: continue subdividing the Data block into a data1 sub-block and a data2 sub-block;

[0066] S3. Skip the data1 sub-block, update the variable nodes in the data2 sub-block and the overlap sub-block in sequence, and search out the data1 sub-block, data2 sub-block, and ov...

PUM

Login to View More

Login to View More Abstract

Description

Claims

Application Information

Login to View More

Login to View More