Super junction device structure and preparation method thereof

A super-junction device and column structure technology, applied in the field of super-junction device structure and its preparation, can solve problems such as difficult to meet the depth of p-column, achieve the effect of optimizing vertical electric field distribution, suitable for large-scale manufacturing, and improving withstand voltage characteristics

- Summary

- Abstract

- Description

- Claims

- Application Information

AI Technical Summary

Problems solved by technology

Method used

Image

Examples

Embodiment 1

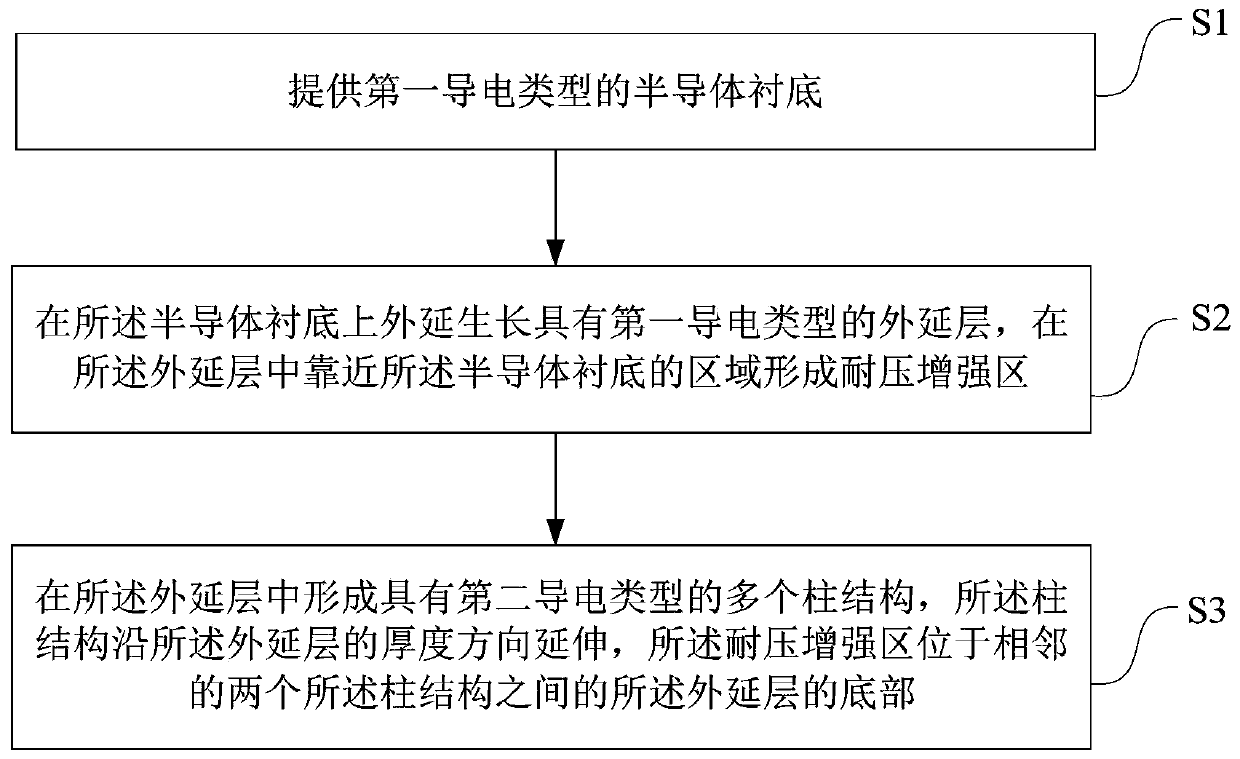

[0066] see Figure 1 to Figure 12 , the invention provides a method for preparing a superjunction device structure, comprising the following steps:

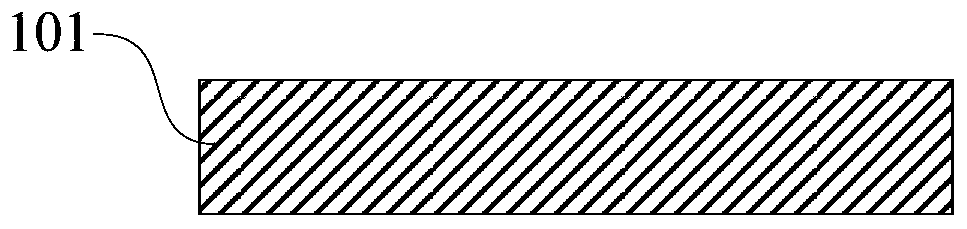

[0067] 1) providing a semiconductor substrate 101 of the first conductivity type;

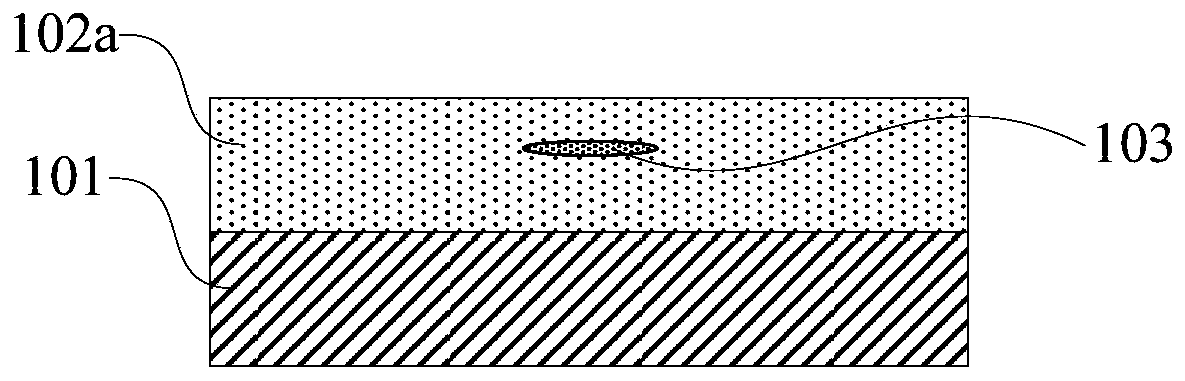

[0068] 2) epitaxially growing an epitaxial layer 102 with a first conductivity type on the semiconductor substrate 101, and forming a withstand voltage enhanced region 103 in a region of the epitaxial layer 102 close to the semiconductor substrate 101

[0069] 3) Forming a plurality of pillar structures 104 with the second conductivity type in the epitaxial layer 102, the pillar structures 104 extending along the thickness direction of the epitaxial layer 102, and the withstand voltage enhanced regions 103 are located in two adjacent The lower part of the epitaxial layer 102 between the pillar structures 104.

[0070] In step 1), see figure 1 The S1 step and figure 2 , providing a semiconductor substrate 101 of the first conductivity type. fi...

Embodiment 2

[0109] This embodiment provides a super-junction device structure and its preparation method. Compared with the trench-type super-junction structure in Embodiment 1, the difference of this embodiment is that this embodiment adopts an epitaxial injection-type super-junction structure, so The pillar structure is formed by multiple epitaxy and implantation.

[0110] As an example, based on the lower epitaxial layer and the enhanced withstand voltage region formed in the first embodiment, when forming the upper epitaxial layer and a plurality of pillar structures with the second conductivity type, first epitaxially grow type of sub-epitaxial layer, and then perform ion implantation and annealing in the region where the column structure is located. After the superposition of multiple sub-epitaxial layers, the multiple sub-epitaxial layers form the upper epitaxial layer, and the implanted regions are aligned and superimposed to form the column structure.

[0111] Other compositions...

PUM

| Property | Measurement | Unit |

|---|---|---|

| Thickness | aaaaa | aaaaa |

| Thickness | aaaaa | aaaaa |

Abstract

Description

Claims

Application Information

Login to View More

Login to View More